AZALEA RAAD, Imperial College London and Meta, UK JOSH BERDINE, Meta, UK DEREK DREYER, MPI-SWS, Germany PETER W. O'HEARN, Meta and University College London, UK

Incorrectness separation logic (ISL) was recently introduced as a theory of under-approximate reasoning, with the goal of proving that compositional bug catchers find actual bugs. However, ISL only considers sequential programs. Here, we develop *concurrent incorrectness separation logic* (CISL), which extends ISL to account for bug catching in concurrent programs. Inspired by the work on Views, we design CISL as a parametric framework, which can be instantiated for a number of bug catching scenarios, including race detection, deadlock detection, and memory safety error detection. For each instance, the CISL meta-theory ensures the *soundness* of incorrectness reasoning for free, thereby guaranteeing that the bugs detected are true positives.

# $\label{eq:CCS} Concepts: \bullet \textbf{Theory of computation} \rightarrow \textbf{Concurrency; Semantics and reasoning; \bullet Software and its engineering} \rightarrow \textbf{General programming languages}.$

Additional Key Words and Phrases: Concurrency, program logics, separation logic, bug catching

#### **ACM Reference Format:**

Azalea Raad, Josh Berdine, Derek Dreyer, and Peter W. O'Hearn. 2022. Concurrent Incorrectness Separation Logic. Proc. ACM Program. Lang. 6, POPL, Article 34 (January 2022), 29 pages. https://doi.org/10.1145/3498695

#### **1 INTRODUCTION**

Recently there has been a successful trend in automated static analysis tools that use *under-approximate* techniques to detect bugs in *concurrent* programs. The idea behind under-approximation is to focus on a *subset* of program behaviours, to ensure one detects only *true positives* (real bugs) rather than *false positives* (spurious bug reports). For instance, RacerD [Blackshear et al. 2018] uses under-approximation to detect data races in Java programs, while Brotherston et al. [2021] utilise under-approximation for deadlock detection. RacerD is the state-of-the-art tool in race detection, significantly outperforming other race detectors in terms of bugs found and fixed: over 3k races found by RacerD have been fixed before reaching production (see [Blackshear et al. 2018]). More significantly, it supported the conversion of Facebook's Android app to a multi-threaded UI model, performing counter-factual reasoning to detect races that could exist *if* a class were placed in a multi-threaded context, *before* it was placed there; thousands of classes were converted this way, leading to performance gains in Facebook's Android app. The deadlock detector of Brotherston et al. [2021] has also been useful in practice, with over two-hundred deadlocks fixed by Facebook engineers. Fixing deadlocks is especially impactful as they can lead to "app not responding" behaviour, which can be more difficult for engineers to detect than plain crashes.

Authors' addresses: Azalea Raad, Imperial College London and Meta, UK, azalea.raad@imperial.ac.uk; Josh Berdine, Meta, UK, josh@berdine.net; Derek Dreyer, MPI-SWS, Saarland Informatics Campus, Germany, dreyer@mpi-sws.org; Peter W. O'Hearn, Meta and University College London, UK, p.ohearn@ucl.ac.uk.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2022 Copyright held by the owner/author(s). 2475-1421/2022/1-ART34 https://doi.org/10.1145/3498695 These static tools are compositional and run quickly on code changes, often in time proportional to the size of a code change rather than that of the global codebase. This distinguishes them from whole-program dynamic testing tools, making them especially well-suited to deployment at code review time within continuous integration systems (a deployment model emphasised by Google and Facebook in articles on static analysis at scale [Sadowski et al. 2018; Distefano et al. 2019]).

Unfortunately, useful though they may be, there is currently no well-understood or unifying theory underpinning such under-approximate analyses. As a result, each time such a tool is developed, the authors spend a significant amount of technical effort proving a *no-false-positives* (NFP) theorem, stating that the bugs found by the tool are indeed real bugs. For instance, in the case of RacerD this took a separate technical effort by Gorogiannis et al. [2019] to establish its NFP theorem. In the case of [Brotherston et al. 2021], the authors have developed a large corpus of lemmas building towards their NFP theorem, requiring significant technical investment and expertise. Furthermore, each such technical effort proves an NFP theorem for a bespoke tool or technique, and one cannot easily port those results to other under-approximate tools or techniques.

Ideally, one would have a unifying theory that underpins *concurrent under-approximate reasoning* (for proving *incorrectness*, i.e. the presence of bugs), in the same way that program logics such as [O'Hearn 2004; Owicki and Gries 1976] provide a foundation for concurrent over-approximate reasoning (for proving *correctness*, i.e. the absence of bugs). The key advantage of such a theory is that tools and techniques underpinned by it are accompanied by an NFP theorem *for free*.

Fortunately, the recent work of O'Hearn [2019] on *incorrectness logic* (IL) and its later extension to *incorrectness separation logic* (ISL) [Raad et al. 2020] have paved the way toward such a theory. IL lays the groundwork for a general theory of compositional under-approximate reasoning, and ISL has extended that to account for pointers and memory errors. However, these logics only apply to *sequential* programs and do not support reasoning about *concurrent* bug catching analyses.

In this paper, we close the gap by extending ISL to support concurrency. This task is far from straightforward, as witnessed in the correctness setting when extending separation logic (SL) [O'Hearn et al. 2001] with concurrency. Specifically, the advent of SL at the turn of the century led to a large body of work extending SL with concurrency, e.g. [O'Hearn 2004; Vafeiadis and Parkinson 2007; Dinsdale-Young et al. 2010; Nanevski et al. 2014; Jung et al. 2015; Raad et al. 2015], using different techniques to address different verification needs. This led to Parkinson's observation, in "The next 700 separation logics" [Parkinson 2010], that there has been "a disturbing trend for each new library or concurrency primitive to require a new separation logic". He rightfully argued "we shouldn't be inventing new separation logics, but should find the right logic to reason about interference". This insight eventually led to the concurrent Views framework [Dinsdale-Young et al. 2013], a parametric meta-theory of concurrent reasoning that distils the essence of separation logic, and can be instantiated to reason about different concurrent scenarios.

In the same spirit, in order to avoid inventing the "next 700 *incorrectness* separation logics", we develop *concurrent incorrectness separation logic* (CISL, pronounced "sizzle"), a unifying framework for concurrent under-approximate reasoning that can be instantiated to prove true-positives theorems for a range of concurrent bug catching scenarios. To our knowledge, CISL is the very *first* formal theory for concurrent under-approximate reasoning and bug catching. As with ISL, a key advantage of CISL is that it supports *compositional* reasoning, as needed to account for compositional analyses like those mentioned above. Moreover, CISL adds compositionality in a new dimension, namely *thread-locality*: we can reason about each concurrent thread in isolation.

Thanks to the soundness of CISL, each CISL instance is automatically accompanied by an NFP theorem. In §4–7, we instantiate CISL to detect concurrency bugs such as data races, deadlocks, and memory safety errors, along with a proof that the bugs found are real. Our CISL instantiations for races and deadlocks are inspired by the under-approximate analyses of RacerD and [Brotherston

|                                                                                                                                                     |  | L':free(x)                |                                      | free(x); $   a := [z];$<br>[z] := 1; $   if (a=1) L: [x]$<br>(c) A data-dependent (gl |                | [ <i>x</i> ] := 1 | 2. un<br>3. [ <i>x</i> ]                 | lock <i>l</i> ;<br>]:= 1;                 | <ul> <li>4. lock <i>l</i>;</li> <li>5. [<i>x</i>] := 2;</li> <li>6. unlock <i>l</i>;</li> <li>(global)</li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------|--------------------------------------|---------------------------------------------------------------------------------------|----------------|-------------------|------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                     |  |                           |                                      | memory safety bug at L                                                                |                |                   | . ,                                      | 0                                         | n lines 3 and 5                                                                                                   |

| 1. lock $l;$ 5. lock $l;$ 2. $[x] := 1;$ 6. $a := [y];$ 3. $[y] := 1;$ 7. unlock $l;$ 4. unlock $l;$ 8. if $(a=1) [x] := 2;$ (e) A non-racy program |  | 2.<br>3.<br>4. u<br>(f) A | [x] := 1<br>[y] := 1<br>inlock $l$ ; | 5. lock l; 6. a:= [1 7. unlock 8. if (*) [ nostic (global and 8                       | l;<br>x] := 2; |                   | := 1;<br>ock <i>l</i> ;<br>= 1;<br>ta-de | 6. <i>a</i> :<br>7.unl<br>8.if(<br>penden | = $[z];$<br>ock $l;$<br>a=1) [x] := 2;<br>t (global) race                                                         |

Fig. 1. Several examples of memory safety bugs and races where all memory locations x, y, z initially hold 0

et al. 2021], respectively. Additionally, we strengthen our instantiations to catch races that RacerD could not, and to produce more informative assertions (i.e. with a witness trace) than those of [Brotherston et al. 2021].

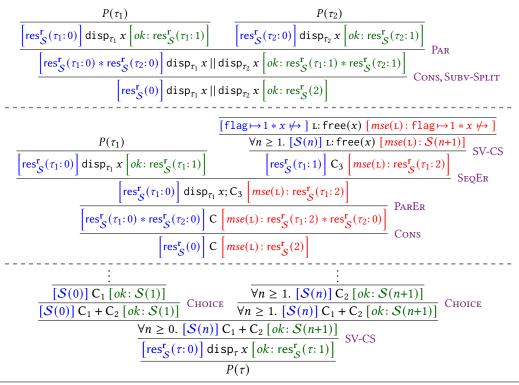

**Contributions and Outline.** Our contributions (detailed in §2) are as follows. In §3 we present the general meta-theory of CISL. In §4 we instantiate CISL for race detection and compare it to RacerD. In §5 we instantiate CISL for deadlock detection and compare it to [Brotherston et al. 2021]. In §6 we further generalise CISL to account for thread interference. Using this generalisation, in §7 we instantiate CISL for subvariant reasoning (an under-approximate analogue of invariant reasoning), and use it to detect memory safety bugs. We discuss related work and conclude in §8.

#### 2 OVERVIEW OF CISL

**CISL at a Glance.** As with its sequential counterpart ISL, CISL allows us to prove triples of the form  $[p] \ C \ [\epsilon : q]$ , stating that *every* state in *q* is reachable by executing C starting in *some* state in *p*. The  $\epsilon$  denotes an *exit condition* that may be either *ok* to denote normal (non-erroneous) execution, or  $\epsilon \in \text{EREXIT}$  to denote a buggy (erroneous) execution (EREXIT is supplied to CISL as a parameter to distinguish different classes of bugs such as memory safety errors, races and so forth). A key part of CISL is its parallel composition rule, PAR in Fig. 5 (p. 9), stating that if we prove  $[p_i] \ C_i \ [ok: q_i]$  for each  $i \in \{1, 2\}$  in isolation, then we can also prove  $[p_1 * p_2] \ C_1 \ [l] \ C_2 \ [ok: q_1 * q_2]$ . Note that PAR is identical to its over-approximate analogue in [O'Hearn 2004] and is similarly *compositional*: we can identify a normal execution of  $C_1 \ [l] \ C_2$  by considering each thread in isolation. Observe that PAR only allows us to prove normal (*ok*) triples; as we describe below, CISL provides different techniques for proving buggy triples, depending on the *bug category*.

The Three Faces of Concurrent Bugs (Errors). When using CISL to detect different classes of bugs (e.g. memory safety errors and races), we have identified three bug categories: 1) *local* (interleaving-agnostic) bugs; 2) *global* (interleaving-dependent), *data-agnostic* bugs; and 3) *global*, *data-dependent* bugs. We describe these three categories through several examples in Fig. 1, where we write  $\tau_1$  and  $\tau_2$  for the left and right threads in each example, respectively.

Local bugs are due to one thread, say  $\tau$ , in that they arise even when  $\tau$  executes in isolation (i.e. sequentially) and are thus *interleaving-agnostic*. An example of this is shown in Fig. 1a: regardless of the behaviour of C in  $\tau_2$  (the right thread), executing  $\tau_1$  (the left thread) leads to a use-after-free (memory safety) bug at L as x is accessed after it is deallocated. As we describe later in §3, local bugs can be detected using the PARER rule of CISL in Fig. 5 (on p. 9): due to the short-circuit semantics of

errors (whereby execution is terminated upon encountering an error), a bug is reached by executing a concurrent program,  $[p] C_1 || C_2 [\epsilon; q]$ , if it is reached by executing one thread,  $[p] C_1 [\epsilon; q]$ .

In contrast to local bugs, global bugs are due to how concurrent threads interact with one another and arise only under certain interleavings, i.e. they are *interleaving-dependent*. For instance, Figures 1b and 1c both depict examples of global bugs. In particular, in an interleaving of Fig. 1b where  $\tau_1$  is executed after (resp. before)  $\tau_2$ , we reach a use-after-free bug at L (resp. L'). Analogously, in an interleaving of Fig. 1c where  $\tau_2$  is executed after  $\tau_1$ , the condition of the if statement is satisfied and thus we reach a use-after-free bug at L. Note that there is a *data dependency* between  $\tau_1$  and  $\tau_2$  in Fig. 1c in that  $\tau_1$  may affect the *control flow* of  $\tau_2$ : the value read in a := [z], and subsequently the condition of if and whether L: [x] := 1 is executed, depends on whether  $\tau_2$  executes a := [z] before or after  $\tau_1$  executes [z] := 1. As such, the bug at L is *data-dependent*. By contrast, the threads in Fig. 1b cannot affect the control flow of one another and thus the bugs at L and L' are *data-agnostic*. Intuitively, data dependence arises through *deterministic* (non-random) conditions in if/loop statements, prescribing a certain execution path. Specifically, were we to replace the (deterministic) condition a=1 in Fig. 1c with the *non-deterministic* expression \* (which evaluates to an arbitrary value), then the memory-safety error at L would be rendered data-agnostic.

**Detecting Global Bugs.** Due to their global nature, global bugs (be they data-agnostic/dependent) cannot be detected using PARER. Instead, as they manifest only under certain interleavings, they can be detected using the PARSEQ, PARL and PARR rules of CISL (in Fig. 5), which enable us to consider certain interleavings. For instance, let  $C_1 = C_3$ ;  $C_4$  and  $C = C_1 || C_2$ , and let  $\epsilon$  denote an error that manifests only in an interleaving of C in which  $C_2$  is executed between  $C_3$  and  $C_4$  as  $[p] C_1 || C_2$  [ $\epsilon : q$ ]. We can then detect  $\epsilon$  as follows. First, we use PARL to execute  $C_3$  normally, (the  $[p] C_3$  [ok: r] premise); and then show that the continuation  $C_4 || C_2$  yields error  $\epsilon$  (the  $[r] C_4 || C_2 [\epsilon : q]$ .

Unfortunately, however, PARSEQ, PARL and PARR are *not compositional* as they consider multiple threads at every proof step, rather than examining each thread in isolation, and require the user to determine an interleaving *a priori*. However, as we discuss below, in most cases we *can* detect global bugs compositionally in CISL by encoding buggy executions as normal ones and then using the compositional PAR rule. We elaborate on this below through several examples of data races.

**Data Races.** Unlike memory safety bugs that may be local or global, *data races* (hereafter simply races) belong solely to the global category. Specifically, two accesses (reads and writes) of a given program C race with one another if 1) they are *conflicting*, i.e. they are by distinct threads, on the same location, and at least one of them is a write; and 2) they appear next to each other in a given interleaving (a.k.a. history) of C. As such, races are attributed to two threads (and are thus global) and may manifest only under certain interleavings. To see this, consider the example in Fig. 1d, and let us write  $H = [1, \dots, n]$  for an interleaving where the instructions numbered  $1 \dots n$  are executed in order. Note that the program in Fig. 1d induces several (partial) interleavings, including H = [1, 2, 4, 3, 5] and H' = [4, 5, 6, 1, 2, 3]. The two conflicting accesses on x (lines 3 and 5) *race* in H as they are adjacent in H. By contrast, they *do not race* in H': thanks to the mutual exclusion induced by the lock on l, they cannot appear as adjacent accesses when  $\tau_2$  acquires l first.

**Data-Dependent Bugs in Practice.** As shown by Blackshear et al. [2018] and Brotherston et al. [2021], data-dependent bugs (due to deterministic conditions in if/while statements) make the task of detecting true bugs (true positives) much more difficult. To see this, consider the example in Fig. 1e and note that it does not allow any data races: both threads access *y* while holding the lock *l*, and  $\tau_2$  accesses *x* only if a = 1, i.e.  $\tau_2$  accesses *x* only when its critical section is executed after that in  $\tau_1$ , forcing a *happens-before* order from [x] := 1 to [x] := 2. On the other hand, it is always

34:5

possible to find a race in Fig. 1f, when the value non-deterministically picked by  $\star$  is non-zero, as witnessed by the history [5, 6, 7, 1, 2, 8]. Note that the program in Fig. 1f only differs from the one in Fig. 1e in that the deterministic condition (*a*=1) is replaced with the non-deterministic  $\star$ .

Although we can generalise the CISL *theory* to detect data-dependent bugs, ruling out datadependent bugs is non-trivial in *practice* (e.g. due to the happens-before order induced under certain interleavings). This difficulty led Blackshear et al. [2018] and Brotherston et al. [2021] to focus only on data-agnostic bugs by assuming that all program conditionals are *non-deterministic* (\*) as in Fig. 1f. As such, in the remainder of the paper, we follow the same practical approach and focus on providing a theoretical foundation for *data-agnostic* bug catching.

**CISL for Detecting Data-Agnostic Bugs.** Returning to Fig. 1d, note that the race between lines 3 and 5 in H = [1, 2, 4, 3, 5] is data-agnostic. As mentioned above, we can detect data-agnostic bugs *compositionally* by treating buggy (here racy) executions as normal (non-erroneous) executions and using the PAR rule to analyse each thread in isolation and combine their results. More concretely, to enable compositional reasoning, we do not treat races as errors. Rather, we compute a local (sequential) history of each thread in isolation, combine them together using PAR, and ultimately examine them to detect data races and construct a global (concurrent) history *witnessing* the race.

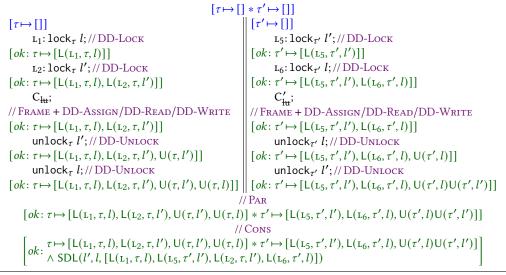

To see this, consider the CISL proof sketch of the race in Fig. 1d in Fig. 2, where the sequential histories of  $\tau_1$ and  $\tau_2$  are initially both [], as denoted by  $\tau_1 \mapsto$  [] \*  $\tau_2 \mapsto$  []. Using PAR, for  $i \in \{1, 2\}$  we reason about  $\tau_i$  in isolation starting from  $\tau_i \mapsto$  []. Subsequently, we obtain  $\tau_1 \mapsto$  [1, 2, 3] and  $\tau_2 \mapsto$  [4, 5, 6] separately, and combine them using PAR into  $\tau_1 \mapsto$  [1, 2, 3] \*  $\tau_2 \mapsto$  [4, 5, 6]. Finally, we use the CISL rule of consequence, Cons, to additionally obtain race(3, 5, [1, 2, 4, 3, 5]), describing a race between lines 3 and 5, witnessed by *global history* [1, 2, 4, 3, 5]. A global history of  $\tau_1 \mapsto H_1$  and  $\tau_2 \mapsto H_2$  is obtained by computing all permutations of  $H_1 # H_2$  (where # denotes concatenation) and then filtering out those that are not *well-formed*.

$$\begin{bmatrix} \tau_1 \mapsto [] & \tau_2 \mapsto [] \\ [\tau_1 \mapsto [] \\ 1. \log k l; \\ [ok: \tau_1 \mapsto [1]] \\ 2. \operatorname{unlock} l; \\ [ok: \tau_1 \mapsto [1, 2]] \\ 3. [x] := 1; \\ [ok: \tau_1 \mapsto [1, 2, 3]] \\ [ok: \tau_1 \mapsto [1, 2, 3] \\ [ok: \tau_2 \mapsto [4, 5, 6]] \\ [ok: \tau_1 \mapsto [1, 2, 3] \\ [ok: \tau_2 \mapsto [4, 5, 6]] \\ [ok: \tau_1 \mapsto [1, 2, 3] \\ [ok: \tau_2 \mapsto [4, 5, 6]] \\ [ok: \tau_1 \mapsto [1, 2, 3] \\ \tau_2 \mapsto [4, 5, 6] \\ [ok: \tau_1 \mapsto (3, 5, [1, 2, 4, 3, 5]) \\ \end{pmatrix} // Cons$$

Intuitively, well-formed histories respect the mutual exclusion semantics of locks. For instance, [1, 4, 2, 3, 5, 6] in Fig. 1d is not well-formed: it allows  $\tau_2$  to acquire l (4) while it is held by  $\tau_1$  (at 1). We formalise well-formed histories in §4.

Lastly, our presentation of histories thus far was abbreviated by merely recording line numbers. However, to identify races, rather than recording line numbers (which requires examining the code), we record execution *events*. For instance, the sequential history of  $\tau_1$  in Fig. 1f is  $\tau_1 \mapsto H_1$  with  $H_1 = [L(\tau_1, l), W(\tau_1, 2, x), W(\tau_1, 3, y), U(\tau_1, l)]$  (abbreviated as [1, 2, 3, 4]), where  $L(\tau_1, l)$  and  $U(\tau_1, l)$  respectively denote (the events for) locking and unlocking *l* on lines 1 and 4, and  $W(\tau_1, 2, x)$  and  $W(\tau_1, 3, y)$  respectively denote writing to *x* and *y* on lines 2 and 3. Similarly, a sequential history of  $\tau_2$  is  $\tau_2 \mapsto H_2$  with  $H_2 = [L(\tau_2, l), R(\tau_2, 6, y), U(\tau_2, l), W(\tau_2, 8, x)]$ . We combine  $H_1$  and  $H_2$  into  $H = [L(\tau_2, l), R(\tau_2, 6, y), U(\tau_2, l), L(\tau_1, l), W(\tau_1, 2, x), W(\tau_2, 8, x)]$ , witnessing the race via the adjacent conflicting accesses  $W(\tau_1, 2, x)$  and  $W(\tau_2, 8, x)$ . Note that we do not record the labels (line numbers) of lock/unlock events: labels are used to locate races which can only occur between memory accesses. Moreover, as we focus on data-agnostic races, we need not record the values read/written. That is, the values read/written do not affect the control flow and have no bearing on races. In the remainder of the paper, we use both abbreviated histories (for exposition brevity) and full histories.

**Summary: Compositional Reasoning with CISL.** CISL proof rules (Fig. 5) support *compositional* reasoning via: (1) PAR for normal executions; and (2) PARER for detecting local bugs. Moreover,

(3) one can detect data-agnostic bugs by encoding buggy executions as normal ones and using PAR to detect them. In the case of (2), PARER reduces *concurrent* bug detection to *sequential*, which can be automated as in [Raad et al. 2020]. In the case of (3), we instantiate CISL to detect races (CISL<sub>RD</sub>), deadlocks (CISL<sub>DD</sub>), and memory safety errors (CISL<sub>SV</sub>); CISL<sub>RD</sub> and CISL<sub>DD</sub> are inspired by the under-approximate analyses of the [Blackshear et al. 2018] and [Brotherston et al. 2021] tools.

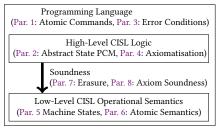

#### **3 THE CISL FRAMEWORK**

We present the CISL meta-theory. The CISL framework is parametric and may be instantiated for concurrent, underapproximate reasoning for a multitude of applications, including e.g.  $\text{CISL}_{\text{DC}}$  (CISL with disjoint concurrency) for detecting memory safety bugs,  $\text{CISL}_{\text{RD}}$  (CISL with race detection) for detecting races on shared memory, and  $\text{CISL}_{\text{DD}}$ (CISL with deadlock detection) for detecting deadlock scenarios. To instantiate CISL, one must supply CISL with the specified parameters; the soundness of the instantiated CISL reasoning then follows immediately from the

Fig. 3. An overview of the CISL framework

soundness of the framework (see Thm. 3.8). For clarity, we delineate the CISL parameters enclosed in solid boxes. To provide a clearer account of CISL, we often follow CISL parameters with their CISL<sub>DC</sub> instantiation for detecting memory safety bugs.

**Programming Language.** We build CISL on a simple programming language comprising standard composite commands, and parametrised by a set of *atomic* commands. This allows us to instantiate CISL for a number of use-cases without changing the underlying meta-theory. Our programming language is given by the C grammar in Def. 3.1, and includes atomic commands (a) supplied as a parameter (Par. 1), as well as the standard constructs of skip, sequential composition  $(C_1; C_2)$ , non-deterministic choice  $(C_1 + C_2)$ , loops  $(C^*)$  and parallel composition  $(C_1 || C_2)$ .

Parameter 1 (Atomic commands). Assume a set of atomic commands, ATOM, ranged over by a.

Definition 3.1 (CISL language). The CISL programming language is defined as follows:

*Example 3.2 (CISL<sub>DC</sub> atomics).* The CISL<sub>DC</sub> atomic commands, ATOM<sub>DC</sub>, are defined as follows:

$ATOM_{DC} \ni a ::= L: error \mid x := v \mid assume(B) \mid x := alloc() \mid L: free(x) \mid L: x := [y] \mid L: [x] := y$

The CISL<sub>DC</sub> atomic commands include explicit error statements (error), assume statements (assume(*B*)) to model deterministic conditionals/loops, assignment (x := v) and heap-manipulating commands for allocation (x := alloc()), disposal (free(x)), lookup (reading from the heap, x := [y]) and mutation (writing to the heap [x] := y). We assume a set BAST of *Boolean assertions*; we use *B* as a metavariable for a Boolean assertion,  $v, v' \cdots$  for values, and x, y, z for variables.

To better track memory safety errors and connect them to culprit instructions, we annotate instructions that may cause such errors with a label  $L \in LABEL$ . As we demonstrate shortly, when an error is encountered we report the label of the offending instruction (e.g. L). As such, we only consider *well-formed* programs: those with unique labels across their constituent instructions. For brevity, we drop the instruction labels when they are immaterial to the discussion.

#### 3.1 CISL Logic and Proof Rules

**State PCM.** Program logics, and reasoning frameworks in general, do not typically reason directly about the low-level machine states. Rather, they provide a high-level (abstract) representation of the state, often equipped with additional instrumentation that supports certain reasoning principles. For instance, in order to reason about concurrent accesses to the memory, one can model the state as a shared heap of memory locations, with each location instrumented with a *fractional permission*  $\pi \in (0, 1]$ , where  $\pi = 1$  on location x denotes *full ownership* on x granting permission for writing to x, while  $0 < \pi < 1$  denotes *partial ownership* on x sufficient for reading from x.

In separation logic and its family of descendants, the high-level states are typically modelled by a *partial commutative monoid* (PCM) of the form (STATE,  $\circ$ , STATE<sup>0</sup>), where STATE denotes the set of states;  $\circ$  : STATE  $\times$  STATE  $\rightarrow$  STATE denotes the partial state composition operator that is commutative and associative; and STATE<sup>0</sup>  $\subseteq$  STATE denotes the set of unit states. The reasoning is then carried out via  $p, q \in$  VIEW  $\triangleq \mathcal{P}($ STATE), describing *views* (sets of states).

Parameter 2 (State PCM). Assume a partial commutative monoid (PCM) for states, (STATE,  $\circ$ , STATE<sup>0</sup>), where STATE<sup>0</sup>  $\subseteq$  STATE and:

- the composition function, : STATE × STATE → STATE, is commutative and associative;

- for all  $s \in STATE$ , there exists  $s_0 \in STATE^0$  such that  $s \circ s_0 = s$ ; and

- for all  $s, s' \in \text{STATE}$  and  $s_0 \in \text{STATE}^0$ , if  $s \circ s_0 = s'$  then s = s'.

*Example 3.3 (CISL*<sub>DC</sub> *States).* We model a CISL<sub>DC</sub> state  $s \in \text{STATE}_{DC}$  as a partial map associating each program variable or location with a value and a *fractional permission*  $\pi \in (0, 1]$ : STATE<sub>DC</sub>  $\triangleq$  (VAR  $\xrightarrow{\text{fin}}$  VAL  $\times (0, 1]$ )  $\cup$  (Loc  $\xrightarrow{\text{fin}}$  (VAL  $\uplus \{\bot\}$ )  $\times (0, 1]$ ). The designated value  $\bot \notin$  VAL is used to track those locations that have been *deallocated*. That is, given  $l \in \text{Loc}$ , if s(l)=(v, -) and  $v \in \text{VAL}$  then l is allocated in s and holds value v; and if  $v=\bot$  then l has been deallocated.

CISL<sub>DC</sub> composition is standard:  $(s_1 \circ_{DC} s_2)(x)$  is 1)  $s_i(x)$  if  $x \in dom(s_i) \setminus dom(s_{3-i})$  for  $i \in \{1, 2\}$ ; 2)  $(v, \pi_1 + \pi_2)$  if  $s_1(x) = (v, \pi_1)$ ,  $s_2(x) = (v, \pi_2)$  and  $\pi_1 + \pi_2 \leq 1$ . If there exists  $x \in dom(s_1) \cap dom(s_2)$  s.t. the conditions of 2) are not satisfied, the entire composition  $s_1 \circ_{DC} s_2$  is undefined. CISL<sub>DC</sub> unit set is STATE<sup>0</sup><sub>DC</sub>  $\triangleq \{\emptyset\}$ , where  $\emptyset$  is an empty function. CISL<sub>DC</sub> state PCM is (STATE<sub>DC</sub>,  $\circ_{DC}$ , STATE<sup>0</sup><sub>DC</sub>).

Definition 3.4 (Views). The set of views is VIEW  $\triangleq \mathcal{P}(\text{STATE})$ .

**Notation.** We use p, q, r as meta-variables for views (i.e.  $p, q, r \in V$ IEW). We write p \* q for  $\{s \circ s' \mid s \in p \land s' \in q\}$ ;  $p \land q$  for  $p \cap q$ ;  $p \lor q$  for  $p \cup q$ ; false for  $\emptyset$ ; and true for VIEW. In the context of CISL<sub>DC</sub>, we write emp for  $\{\emptyset\}$  and  $l \stackrel{\pi}{\mapsto} v$  (resp.  $x \stackrel{\pi}{\mapsto} v$ ) for  $\{[l \mapsto (v, \pi)]\}$  (resp.  $\{[x \mapsto (v, \pi)]\}$ ). We write  $l \mapsto v$  (resp.  $x \mapsto v$ ) for  $l \stackrel{1}{\mapsto} v$  (resp.  $x \stackrel{1}{\mapsto} v$ ),  $l \stackrel{\pi}{\not\mapsto}$  for  $l \stackrel{\pi}{\mapsto} \bot$ , and  $l \not\mapsto$  for  $l \stackrel{1}{\not\mapsto}$ .

**Exit Conditions.** The CISL theory uses *under-approximate triples* [O'Hearn 2019] of the form  $[p] C [\epsilon : q]$ , interpreted as: *q* describes a *subset* of the states that can be reached from *p* by executing C, where  $\epsilon$  denotes an *exit condition* indicating either normal or erroneous termination.

We define the set of exit conditions as EXIT  $\triangleq \{ok\} \uplus \text{EREXIT}$ , where ok denotes normal termination, and  $\epsilon \in \text{EREXIT}$  denotes an erroneous termination. Erroneous conditions are reasoning-specific and thus supplied as a CISL parameter. For instance, an error condition in  $\text{CISL}_{\text{DC}}$  denotes either a memory safety bug or an explicit error (after executing error). Concretely, we define  $\text{CISL}_{\text{DC}}$  error conditions as  $\text{EREXIT}_{\text{DC}} \triangleq \{mse(L), er(L) \mid L \in \text{LABEL}\}$ , where mse(L) denotes a memory safety bug encountered at the L-labelled instruction and er(L) denotes an explicit error at L.

*Parameter 3 (Error conditions).* Assume a set of *error conditions*, EREXIT, where  $ok \notin$  EREXIT.

**Atomic Axioms.** We shortly define the under-approximate proof system of CISL. As atomic commands are supplied as a parameter, the CISL proof system is accordingly parametrised by their set of under-approximate *axioms* (Par. 4). An atomic axiom is a tuple of the form  $(p, a, \epsilon, q)$ , with  $p, q \in VIEW$ ,  $a \in ATOM$  and  $\epsilon \in EXIT$ , and is lifted to the CISL proof rule [p] a  $[\epsilon : q]$  (see ATOM).

*Parameter 4 (Axioms).* Assume a set of *axioms* AXIOM  $\subseteq$  VIEW × ATOM × EXIT × VIEW.

*Example 3.5 (CISL*<sub>DC</sub> axioms). The CISL<sub>DC</sub> axioms, AXIOM<sub>DC</sub>, are given in Fig. 4 and are analogous to those of Raad et al. [2020]. For better readability, we present the axioms as inference rules with CISL triples of the form [p] a  $[\epsilon : q]$  in their conclusion, rather than tuples of the form  $(p, a, \epsilon, q)$ .

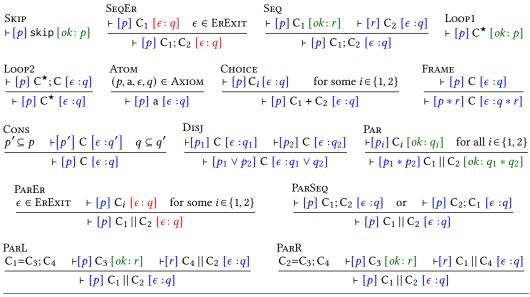

**CISL Proof Rules.** We present the under-approximate CISL proof system in Fig. 5. As in [Raad et al. 2020; O'Hearn 2019], our triples are of the form:  $\vdash [p] C [\epsilon : q]$ , denoting that every state in the postcondition q is reachable from some state in the precondition p under  $\epsilon$ . That is, for each  $s_q$  in q, there exists  $s_p$  in p such that executing C on  $s_p$  terminates with  $\epsilon$  and yields  $s_q$ .

The SKIP, SEQER, SEQ, LOOP1, LOOP2, CHOICE, CONS and DISJ rules are as in [O'Hearn 2019; Raad et al. 2020]). Similarly, the FRAME rule is analogous to that of [Raad et al. 2020], except that the \* operator here denotes the general notion of composition defined by lifting the composition operator of the underlying PCM to views (sets of states), rather than that of heap composition in [Raad et al. 2020].

The ATOM rule simply lifts atomic axioms as CISL proof rules. The PAR rule is an under-approximate analogue of the disjoint concurrency rule in concurrent separation logic (CSL) [O'Hearn 2004], stating that if the states in  $q_1$  (resp.  $q_2$ ) are reachable from those in  $p_1$  (resp.  $p_2$ ) when executing  $C_1$  (resp.  $C_2$ ), then the combined states in  $q_1 * q_2$  are reachable from  $p_1 * p_2$  when executing  $C_1 || C_2$ . Note that, unlike in CSL where the composition operator imposes *disjointness*, the composition operator in CISL does not and merely mandates composability as defined by the PCM (Par. 2).

The PARER rule is the concurrent analogue of SEqER, describing the *short-circuiting* semantics of concurrent executions: given  $i \in \{1, 2\}$ , if running the smaller program  $C_i$  results in an error, then running the larger  $C_1 || C_2$  also results in an error. Intuitively, this is because the behaviours of  $C_1$ ;  $C_2$  and  $C_2$ ;  $C_1$  are both included in those of  $C_1 || C_2$ , in that they describe two possible *interleavings* when executing  $C_1 || C_2$ . As such, as in SEqER, if running  $C_1$  (resp.  $C_2$ ) yield an error, then the overall execution of the  $C_1$ ;  $C_2$  (resp.  $C_2$ ;  $C_1$ ) interleaving of  $C_1 || C_2$  also yields an error.

Fig. 5. The CISL proof rules

Finally, PARL, PARR and PARSEQ are concurrent analogues of SEQ, stating that the states in q are reachable from those in p by executing  $C_1 || C_2$ , if they are reachable under a particular *interleaving* of  $C_1 || C_2$ . For instance, when  $C_1 = C_3$ ;  $C_4$ , PARL captures the  $C_3$ ;  $(C_4 || C_2)$  interleaving of  $C_1 || C_2$ : if executing  $C_3$  from p terminates normally and yields  $r (\vdash [p] C_3 [ok: r])$  and executing the continuation  $C_4 || C_2$  from r yields q under  $\epsilon$ , then executing  $C_1 || C_2$  from p results in q under  $\epsilon$ . Observe that PAR can be *derived* from PARSEQ, SEQ and FRAME as follows:

$$\frac{\begin{matrix} \vdash [p_1] C_1 [ok; q_1] \\ \vdash [p_1 * p_2] C_1 [ok; q_1 * p_2] \end{matrix}}{\vdash [p_1 * p_2] C_1 [ok; q_1 * p_2] } F_{RAME} & \frac{\vdash [p_2] C_2 [ok; q_2] \\ \vdash [q_1 * p_2] C_2 [ok; q_1 * q_2] \end{matrix}}{\vdash [p_1 * p_2] C_1; C_2 [ok; q_1 * q_2]} F_{RAME} \\ \frac{\vdash [p_1 * p_2] C_1; C_2 [ok; q_1 * q_2] }{\vdash [p_1 * p_2] C_1 || C_2 [ok; q_1 * q_2]} P_{ARSEQ}$$

Note that the PAR rule enables *compositional* reasoning in that it is *interleaving-agnostic*, allowing us to reason about the behaviour of each thread in isolation, i.e. locally, combining the results at the end. Intuitively, this is because of the resources accessed by distinct threads are compatible with one another, then their combined result is reachable regardless of their interleaving. That is, the combined result is reachable under *all* possible interleavings of concurrent threads. Similarly, PARER enables compositional bug-catching by allowing us to reason about the erroneous behaviour of one thread in isolation. This is thanks to the short-circuiting semantics of CISL for concurrent executions: if one thread terminates erroneously, then the overall program also terminates erroneously. By contrast, PARL, PARR and PARSEQ are not compositional and correspond to a particular interleaving.

As discussed in §2, PARER is used to detect *local* bugs, i.e. those bugs that are *interleaving-agnostic* and can manifest by executing a single thread, regardless of the behaviour of concurrent threads. For instance, when concurrent threads access disjoint heap resources, then memory safety bugs such as use-after-free are instances of local bugs: if a thread  $\tau$  accesses a memory location owned by  $\tau$  after it has already been freed (deallocated) by  $\tau$ , then a use-after-free error can always be encountered regardless of the behaviour of other threads running concurrently with  $\tau$ .

However, as discussed in §2, certain bugs are *global* (i.e. they depend on the behaviour of two or more threads) and are *interleaving-dependent* in that they only manifest under certain interleavings. For instance, data races and deadlocks are examples of bugs that may only occur under certain interleavings of two or more threads. As such, PARER cannot be used to detect such global bugs. Although PARL and PARR can indeed be used to detect global bugs such as data races, they are not ideal due to their non-compositionality. However, as discussed in §2, we can detect (global) data-agnostic errors *compositionally* by encoding *bugs as non-errors*, whereby we treat buggy executions as normal (non-erroneous) ones and use PAR to analyse them compositionally. As such, we show that PAR and PARER are indeed sufficient to detect a significant number of bugs compositionally.

#### 3.2 CISL Model and Semantics

We next present the CISL operational semantics, parametrised by *machine states* (Par. 5 below). Note that while the states in Par. 2 provide a high-level (often instrumented) state representation, the machine states denote a low-level representation of the machine (without instrumentation). For instance,  $\text{CISL}_{DC}$  machine states forgo the fractional instrumentation of their high-level counterpart.

Parameter 5 (Machine states). Assume a set of machine states, MSTATE, ranged over by m.

*Example 3.6 (CISL<sub>DC</sub> machine states).* A CISL<sub>DC</sub> machine state  $m \in MSTATE_{DC}$  is a partial function from variables and locations to VAL  $\uplus \{\bot\}$ : MSTATE<sub>DC</sub> : (VAR  $\stackrel{\text{fin}}{\rightarrow}$  VAL)  $\cup$  (Loc  $\stackrel{\text{fin}}{\rightarrow}$  VAL  $\uplus \{\bot\}$ ).

**Atomic Semantics.** As the set of atomic commands is supplied as a parameter to the CISL programming language (Par. 1), the CISL operational semantics is further parametrised by the *semantics of atomic commands* (Par. 6 below), defined as (machine) state transformers. For instance, the CISL<sub>DC</sub> atomic semantics is analogous to its counterpart in [Raad et al. 2020].

Parameter 6 (Atomic semantics). Assume an atomic semantics function  $[\![.]\!]_A : ATOM \to EXIT \to \mathcal{P}(MSTATE \times MSTATE).$

**CISL operational semantics.** We define the CISL operational semantics by separating its *control flow transitions* from its state-transforming transitions. The former describe the sequential execution steps in each thread, e.g. how a loop is unrolled; while the latter describe how the underlying machine states determine the overall execution of a (concurrent) program.

The CISL control flow transitions at the top of Fig. 6 are standard and are of the form  $C \xrightarrow{l} C'$ , where  $l \in LAB \triangleq ATOM \uplus \{id\}$  denotes the *transition label*. A transition label l may be either id for silent transitions (no-ops), or  $a \in ATOM$  for executing the atomic command a.

We define the *state-transforming function*  $[\![.]\!]$  : LAB  $\rightarrow \text{EXIT} \rightarrow \mathcal{P}(\text{MSTATE} \times \text{MSTATE})$  as an extension of  $[\![.]\!]_A$  as follows. Given a transition label l, we write  $[\![l]\!]\epsilon$  for 1)  $[\![l]\!]_A\epsilon$  when  $l \in \text{ATOM}$ ; 2) { $(m, m) \mid m \in \text{MSTATE}$ } when l = id and  $\epsilon = ok$ ; and 3) Ø when l = id and  $\epsilon \in \text{EREXIT}$ . That is, atomic transitions transform the state according to their semantics as prescribed by  $[\![.]\!]_A$  (Par. 6), while no-op transitions (denoted by id) always execute normally and leave the state unchanged.

The CISL state-transforming transitions are given at the bottom of Fig. 6 and are of the form  $C, m \stackrel{n}{\Rightarrow} \epsilon, m'$  with  $C \in COMM, m, m' \in MSTATE, \epsilon \in EXIT$  and  $n \in \mathbb{N}$ , stating that starting from state m, program C terminates after n steps in state m' under exit condition  $\epsilon$ . The first transition states that skip trivially terminates (after zero steps) successfully (with exit condition ok) and leaves the underlying state unchanged. The second transition states that starting from m a program C terminates erroneously (with  $\epsilon \in EREXIT$ ) after one step in m' if it takes an erroneous step. Finally, the last (inductive) transition states that if C takes one normal (non-erroneous) step transforming

$$\frac{1}{a \xrightarrow{a} \text{skip}} \frac{C_1 \xrightarrow{l} C'_1}{C_1; C_2 \xrightarrow{l} C'_1; C_2} = \frac{1}{\text{skip}; C \xrightarrow{id} C} \frac{i \in \{1, 2\}}{C_1 + C_2 \xrightarrow{id} C_i} = \frac{i \in \{1, 2\}}{C_1 + C_2 \xrightarrow{id} C_i} = \frac{1}{C^* \xrightarrow{id} skip} = \frac{1}{C^* \xrightarrow{id} C; C^*}$$

$$\frac{1}{C_1 \xrightarrow{l} C'_1} \frac{C_1 \xrightarrow{l} C'_1}{C_1 \parallel C_2} = \frac{C_2 \xrightarrow{l} C'_2}{C_1 \parallel C_2 \xrightarrow{l} C_1 \parallel C'_2} = \frac{1}{\text{skip} \parallel C} = \frac{1}{C'} = \frac{1}{C'}$$

Fig. 6. The CISL control flow transitions (above); the CISL operational semantics (below)

*m* to *m*<sup> $\prime\prime$ </sup>, and the resulting program C<sup> $\prime\prime$ </sup> subsequently terminates after *n* steps with  $\epsilon$  transforming *m*<sup> $\prime\prime$ </sup> to *m*<sup> $\prime$ </sup>, then the overall program terminates after *n*+1 steps with  $\epsilon$  transforming *m* to *m*<sup> $\prime$ </sup>.

#### 3.3 CISL Soundness

**Erasure.** In order to relate the CISL proof system to its operational semantics, it is necessary to define a relationship between the abstract states and the concrete machine states. To this end, as the abstract and machine states are both supplied as parameters to CISL, we further parametrise CISL by an *erasure* function, relating each abstract state to a set of machine states. For instance, in the case of CISL<sub>DC</sub>, the erasure function simply removes the instrumentation given by permissions.

*Parameter 7 (Erasure).* Assume an *erasure function*  $\lfloor . \rfloor$  : STATE  $\rightarrow \mathcal{P}(MSTATE)$ .

We lift the erasure function to views (sets of states) and define  $\lfloor p \rfloor \triangleq \bigcup_{s \in p} \lfloor s \rfloor$  for  $p \in VIEW$ .

*Example 3.7 (CISL*<sub>DC</sub> *erasure).* The  $CISL_{DC}$  *erasure function*,  $\lfloor . \rfloor_{DC}$ , is defined as follows: where:

$$\lfloor s \rfloor_{\mathsf{DC}} = \{ m \} \iff dom(m) = dom(s) \land \forall x, v. \ m(x) = v \implies s(x) = (v, -)$$

**Semantic Incorrectness Triples.** We next present the formal interpretation of CISL triples. Recall that intuitively a CISL triple  $[p] C [\epsilon : q]$  states that every state in q is reachable from some state in p under  $\epsilon$ . Put formally:  $\models [p] C [\epsilon : q] \stackrel{\text{def}}{\longleftrightarrow} \exists n \in \mathbb{N}$ . reach<sub>n</sub> $(p, C, \epsilon, q)$ , denoting that each state in q is reachable from some state in p in at most n steps, with:

$$\operatorname{reach}_n(p,\mathsf{C},\epsilon,q) \ \stackrel{\mathrm{def}}{\longleftrightarrow} \ \forall m_q \in \lfloor q \rfloor. \ \exists m_p \in \lfloor p \rfloor, k \leq n. \ \mathsf{C}, m_p \xrightarrow{k} \epsilon, m_q$$

Atomic Soundness. In order to show that the CISL proof system is sound, we must show that its (syntactic) triples in Fig. 5 induce valid semantics triples: if a triple  $\vdash [p] C [\epsilon :q]$  is derivable using the rules in Fig. 5, then  $\models [p] C [\epsilon :q]$  holds. Note that we must also show this for the atomic axioms in Par. 4 as they are lifted to proof rules via ATOM. Since atomic axioms are a CISL parameter, we thus require (Par. 8 below) that they 1) induce valid semantic triples; and 2) preserve all \*-compatible views. The former ensures that if  $(p, a, \epsilon, q) \in AXIOM$ , then  $\models [p] a [\epsilon :q]$  holds; i.e. for all  $m_q \in \lfloor q \rfloor$ , there exists  $m_p \in \lfloor p \rfloor$  such that  $(m_p, m_q) \in \llbracket a \rrbracket_A \epsilon$ . The latter ensures that atomic commands of one thread preserve the states of concurrent threads in the environment and is necessary for establishing the soundness of FRAME. Putting the two conditions together, we require: Parameter 8 (Atomic soundness). Assume that for all  $(p, a, \epsilon, q) \in AXIOM$  the following holds:  $\forall s \in STATE, m_q \in \lfloor q * \{s\} \rfloor$ .  $\exists m_p \in \lfloor p * \{s\} \rfloor$ .  $(m_p, m_q) \in \llbracket a \rrbracket_A \epsilon$

We show the soundness of the CISL<sub>DC</sub> atomic axioms in the technical appendix [Raad et al. 2022]. Finally, in the following theorem we show that the CISL proof system is *sound*, with its full proof given in the technical appendix [Raad et al. 2022].

THEOREM 3.8 (SOUNDNESS). For all  $p, C, \epsilon, q, if \vdash [p] C [\epsilon : q]$  is derivable using the rules in Fig. 5, then  $\models [p] C [\epsilon : q]$  holds.

#### 3.4 Generalising the Rule of Consequence (View Shifts)

**View Shifts.** As shown in the literature [Dinsdale-Young et al. 2013; Jung et al. 2015], it is common to instrument abstract states with additional *ghost* states (e.g. auxiliary variables [Owicki and Gries 1976]) that do not have a counterpart in the underlying machine states. As such, when updating the ghost state, one can alter the abstract state without changing the underlying machine state. To capture such updates, following the literature we define a *view shift* relation. A view shift from abstract states *p* to those in *q*, written  $p \leq q$ , describes updating each abstract state  $s_p \in p$  to some abstract state  $s_q \in q$  without altering the underlying machine state and while preserving all \*-compatible states (i.e. frames). This is captured in Def. 3.9 below. We can then *generalise* the rule of consequence Cons in Fig. 5 to use view shifts in its premise rather than implications, as shown in GCons below. In the technical appendix [Raad et al. 2022] we show that GCons is sound.

$$\frac{p' \leq p \quad \vdash [p'] C [\epsilon : q'] \quad q \leq q'}{\vdash [p] C [\epsilon : q]}$$

Definition 3.9 (View shift). The view shift relation,  $\leq \subseteq$  VIEW × VIEW, is defined as follows:

$$p \leq q \iff \forall s \in \text{STATE.} \lfloor p * \{s\} \rfloor \subseteq \lfloor q * \{s\} \rfloor$$

#### 4 CISL<sub>RD</sub>: CISL FOR RACE DETECTION

We present  $\text{CISL}_{\text{RD}}$  for detecting data-agnostic races such as that in Fig. 1f. We follow the approach of the RacerD tool [Blackshear et al. 2018] and assume all program conditions are non-deterministic. We compare  $\text{CISL}_{\text{RD}}$  with RacerD and show how it detects races that RacerD cannot.

**Lazy versus Eager Race Reporting.** Recall from §2 that we use  $\text{CISL}_{\text{RD}}$  to detect races by encoding erroneous (here racy) executions as normal ones. This has an additional advantage in that it allows us to uncover *all* potential races at once. More concretely, when combining the sequential histories of threads, we can either adopt a *lazy* approach where we only report the first global history that witnesses a race, or adopt an *eager* approach where we consider and find a witness for each possible race. For instance, let C denote extending the program in Fig. 1d with a third thread  $\tau_3$  executing 7. [x] := 3, thus yielding the sequential history [7]. The lazy approach then produces a trace witnessing a single race, e.g. [1, 2, 3, 7], whereas the eager approach produces a witness trace for each of the three data races, namely between lines 3 and 5 (witness [1, 2, 4, 3, 5]), lines 3 and 7 (witness [1, 2, 3, 7]).

**Simplifying Assumption: Races.** As CISL (and by extension  $\text{CISL}_{RD}$ ) is an under-approximate analysis, it is sound to aim for a subset of races. As such, for simplicity, rather than aiming to detect all races, we initially focus on a specific class of races. Specifically, we target races between conflicting accesses *e* and *e'* where the set of locks held by at least one access is empty. This way, given two sequential histories of the form  $H = H_0 + e + -$  and  $H' = H'_0 + e' + -$ , when the set of locks

$$\begin{split} H &\in \mathrm{Hist} \triangleq \left\{ E \in \mathrm{Seq}\langle \mathrm{Event} \rangle \mid \mathsf{wf}(E) \right\} \qquad e \in \mathrm{Event} \triangleq \begin{cases} \mathsf{R}(\mathsf{L},\tau,x), \mathsf{W}(\mathsf{L},\tau,x), \mid \mathsf{L} \in \mathrm{LabeL} \land \tau \in \mathrm{TID} \\ \mathsf{L}(\tau,x), \mathsf{U}(\tau,x) \mid \land x \in \mathrm{Loc} \end{cases} \\ s \in \mathrm{STATE}_{\mathrm{RD}} \triangleq \left\{ f \in \mathrm{TID} \stackrel{\mathrm{fin}}{\longrightarrow} \mathrm{Hist} \mid \forall \tau, H, e. \ f(\tau) = H \land e \in H \Rightarrow \mathrm{tid}(e) = \tau \right\} \qquad m \in \mathrm{MSTATE}_{\mathrm{RD}} \triangleq \mathrm{Hist} \\ \mathsf{wf}(H) \stackrel{\mathrm{def}}{\longleftrightarrow} \forall x, \tau, H'. \ H = H' + \mathsf{U}(\tau, x) + - \Longrightarrow x \in \mathrm{alocks}(H', \tau) \\ \land \forall x, \tau, H'. \ H = H' + \mathsf{L}(\tau, x) + - \Longrightarrow \forall \tau'. \ x \notin \mathrm{alocks}(H', \tau') \\ \mathsf{alocks}([], \tau) \triangleq \emptyset \qquad \mathsf{alocks}(e + H, \tau) \triangleq \begin{cases} \{x\} \cup \mathrm{alocks}(H, \tau) & \mathsf{if} \ e = \mathsf{L}(\tau, x) \land \mathsf{U}(\tau, x) \notin H \\ \mathsf{alocks}(H, \tau) & \mathsf{otherwise} \end{cases} \end{split}$$

Fig. 7. The  $CISL_{RD}$  model domain

held at *e* is empty, then we can always construct the well-formed *witness* history  $H_0 + H'_0 + e + e'$ . For instance, when *e* and *e'* respectively denote the accesses on lines 3 and 5 of Fig. 1d, then the set of locks held by  $\tau_1$  at *e* is empty. As such, given the sequential histories H = [1, 2, 3] and H' = [4, 5, 6], we can construct the history [1, 2, 4, 3, 5] witnessing the race, i.e.  $H_0 = [1, 2]$  and  $H'_0 = [4]$ . As we describe shortly in §4.1, this is because when the set of locks held at *e* is empty (i.e.  $H_0$  contains no active locks), then the history  $H_0 + H'_0 + e + e'$  is always well-formed.

**Caveat and Relation to RacerD.** The subset of racy executions described above coincide precisely with those detected by RacerD [Blackshear et al. 2018]. Nevertheless, both our simple approach described above and RacerD fail to detect races where e.g. two threads with conflicting accesses hold a disjoint set of

1.

$$\operatorname{lock}_{\tau} l;$$

2.  $\operatorname{L:} [x] :=_{\tau} 1;$

3.  $\operatorname{unlock}_{\tau} l;$

(RACE1)

4.  $\operatorname{lock}_{\tau'} l';$

5.  $\operatorname{L':} [x] :=_{\tau'} 2;$

6.  $\operatorname{unlock}_{\tau'} l';$

locks, as shown in RACE1. Specifically, as the two threads acquire two distinct locks (l and l'), RACE1 induces the racy interleaving H = [1, 4, 2, 5] in which the conflicting accesses on x (on lines 2 and 5) are adjacent. However, neither RacerD nor our simple CISL<sub>RD</sub> instantiation detect this race. Nevertheless, in §4.2 we show how we can generalise and strengthen CISL<sub>RD</sub> to detect such races.

#### 4.1 CISL<sub>RD</sub> Formalism

**CISL**<sub>RD</sub> **Atomic Commands (Par. 1).** We assume a set of shared memory locations ranged over by *x*, *y*, *l*, and a set of local variables (registers) ranged over by *a*, *b*, *c*. We instantiate  $\text{CISL}_{\text{RD}}$  with a simple set of atomic commands comprising reads and writes (accesses) on shared memory locations, and locking constructs used as a synchronisation mechanism to avoid races:

ATOM<sub>RD</sub>

$$\ni$$

a ::= L:  $a :=_{\tau} [x] \mid L: [x] :=_{\tau} a \mid lock_{\tau} l \mid unlock_{\tau} l$

To identify races, we annotate instructions with a thread id  $\tau$ . Moreover, to locate races we further annotate memory accesses with a label L. As such, we assume that a CISL<sub>RD</sub> program C is *well-formed* in that (1) the labels across C are unique; (2) instructions of the same thread are associated with the same thread id; and (3) concurrent instructions in C have distinct thread ids.

Note that ATOM<sub>RD</sub> does not include the assume(.) construct, and thus since the CISL programming language (Def. 3.1) only supports non-deterministic choice ( $C_1 + C_2$ ) and loops ( $C^*$ ), we rule out deterministic conditionals and loops from CISL<sub>RD</sub>.<sup>1</sup>

**CISL**<sub>RD</sub> **State PCM (Par. 2).** The CISL<sub>RD</sub> states, STATE<sub>RD</sub>, are as defined in Fig. 7, where a state *s* is a map from thread identifiers to *well-formed histories*. A history records a sequence of *events* executed by the thread thus far, where an event may be either 1) R(L,  $\tau$ , x) denoting a read access on x by  $\tau$  at L; 2) W(L,  $\tau$ , x) denoting a write access on x by  $\tau$  at L; 3) L( $\tau$ , l) denoting a lock acquisition

<sup>&</sup>lt;sup>1</sup>Recall that if (b) then  $C_1$  else  $C_2$  can be encoded as (assume(b);  $C_1$ ) + (assume(¬b);  $C_2$ ), and while (b) C can be encoded as (assume(b); C)\*; assume(¬b).

on *l* by  $\tau$ ; or 4) U( $\tau$ , *l*) denoting a lock release on *l* by  $\tau$ . The functions tid and lab respectively return the thread and label of an event, where applicable; e.g. tid(e) =  $\tau$  and lab(e) = L when  $e = R(L, \tau, x)$ .

A history is well-formed, written wf(H), iff it respects the lock semantics. Specifically, if H contains a lock release on x by  $\tau$ , then it must contain an earlier lock acquisition on x by  $\tau$  (first conjunct); i.e. a lock can only be released by the thread that acquired it last. Moreover, if H contains a lock acquisition on x by  $\tau$ , then no thread must have previously acquired x without releasing it (second conjunct). Note that given a history H and a thread  $\tau$ , the alocks(H,  $\tau$ ) denotes the *active locks* of  $\tau$  in H, namely those locks that have been acquired by  $\tau$  in H but not released.

The CISL<sub>RD</sub> PCM is (STATE<sub>RD</sub>,  $\forall$ ,  $\emptyset$ ), where  $\forall$  denotes disjoint function union and  $\emptyset$  denotes a map with an empty domain. We write  $\tau \mapsto H$  for the set  $p=\{[\tau \mapsto H]\}$ . We define the *conflict* relation,  $\bowtie$ , as follows, where  $R^{s}$  denotes the symmetric closure of R:

$$\mathbf{\bowtie} \triangleq \left( (\text{Event} \times \text{Event}) \cap \left\{ (\mathsf{R}(\mathsf{l}, \tau, x), \mathsf{W}(\mathsf{l}', \tau', x)), (\mathsf{W}(\mathsf{l}, \tau, x), \mathsf{W}(\mathsf{l}', \tau', x)) \mid \tau \neq \tau' \right\} \right)^{s}$$

CISL<sub>RD</sub> Error Conditions (Par. 3). As discussed above, we do not treat data races as errors and thus define the set of erroneous exit conditions for  $CISL_{RD}$  as the empty set:  $EREXIT_{RD} \triangleq \emptyset$

**The Race Assertion.** Recall from §4 that we aim to detect races between conflicting accesses  $e_1$  and  $e_2$  where the set of locks held by at least one access is empty. This is captured by race( $L_1$ ,  $L_2$ , H) below, denoting a data race between  $L_1$  and  $L_2$  with the *witness history* (trace) H:

$$\operatorname{race}(L_1, L_2, H) \iff \exists \tau_1, \tau_2, e_1, e_2, H_1, H_2. \ \tau_1 \mapsto H_1 \ \# \ e_1 \ \# \ - \ast \ \tau_2 \mapsto H_2 \ \# \ e_2 \ \# \ - \ast \ e_1 \bowtie \ e_2 \\ \ast \ \operatorname{lab}(e_1) = L_1 \ \ast \ \operatorname{lab}(e_2) = L_2 \ \ast \ \operatorname{alocks}(H_1, \tau_1) = \emptyset \ \ast \ H = H_1 \ \# \ H_2 \ \# \ [e_1, e_2]$$

Specifically, if the history of  $\tau_1$  is of the form  $H_1 + e_1 + -$  with  $e_1$  at  $L_1$ , the history of  $\tau_2$  is  $H_2 + e_2 + -$  with  $e_2$  at  $L_2$ , the accesses  $e_1$  and  $e_2$  are conflicting, and (without loss of generality) the set of locks held by  $\tau_1$  prior to  $e_1$  is empty, then there is a race between  $e_1$  and  $e_2$  which can be witnessed by  $H_1 + H_2 + [e_1, e_2]$ . For instance, let  $e_i$  denote the event associated with the instruction on line *i* in Fig. 1d; i.e.  $e_3$  and  $e_5$  denote the conflicting accesses on lines 3 and 5, respectively. Then race(3, 5,  $[e_1, e_2, e_4, e_3, e_5]$ ) holds, capturing the race between  $e_3$  and  $e_5$ .

Note that requiring that  $\tau_1$  hold an empty lock set upon the  $e_1$  access simplifies the task of constructing a witness history. Specifically, as the set of locks held by  $\tau_1$  at the end of  $H_1$  is empty, the combined history  $H_1 + H_2 + [e_1, e_2]$  is always well-formed (see Fig. 7). We shortly demonstrate how race can be used for identifying races in an execution.

**CISL**<sub>RD</sub> **Axioms (Par. 4).** The CISL<sub>RD</sub> axioms, AXIOM<sub>RD</sub>, are defined below, where assignments require no resource (they do not extend the history as their behaviour is local), while each non-local instruction of  $\tau$  simply extends its history thus far with an associated event. For instance, when the current state is  $\tau \mapsto H$ , i.e. the current history of  $\tau$  is given by H, then executing lock<sub> $\tau$ </sub> l updates the state to  $\tau \mapsto H + L(\tau, l)$ . Note that when  $\tau$  already holds the lock on l (i.e.  $l \in alocks(H, \tau)$ ), then the resulting history  $H + L(\tau, l)$  is not well-formed, and thus  $\tau \mapsto H + L(\tau, l)$  describes an empty set, rendering the triple vacuously true. For better readability, we present the axioms as inference rules with CISL triples of the form [p] a  $[\epsilon : q]$ , rather than tuples of the form  $(p, a, \epsilon, q)$ .

$\begin{array}{l} \text{RD-READ} & \text{RD-WRITE} \\ [\tau \mapsto H] \text{ L: } a :=_{\tau} [x] [ok: \tau \mapsto H + \text{R}(\textbf{L}, \tau, x)] & [\tau \mapsto H] \text{ L: } [x] :=_{\tau} a [ok: \tau \mapsto H + \text{W}(\textbf{L}, \tau, x)] \\ \end{array}$   $\begin{array}{l} \text{RD-ASSIGN} & \text{RD-Lock} & \text{RD-UNLOck} \\ [\text{emp}] x := \text{e} [ok: \text{emp}] & [\tau \mapsto H] \text{ lock}_{\tau} l [ok: \tau \mapsto H + \text{L}(\tau, l)] & [\tau \mapsto H] \text{ unlock}_{\tau} l [ok: \tau \mapsto H + \text{U}(\tau, l)] \end{array}$

Fig. 8. A proof sketch of the race in Fig. 1f (see Example 4.2)

*Example 4.1.* Let  $e \triangleq W(L, \tau, x)$  and  $e' \triangleq W(L', \tau', x)$ . We then have:

| $[\tau \mapsto []] L: [x] :=_{\tau} 1 [ok: \tau \mapsto [e]] RD-WRITE$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\overline{[\tau' \mapsto []]} \operatorname{L}': [x] :=_{\tau'} 2 [ok: \tau' \mapsto [e']$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RD-WRITE |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| $\frac{[\tau \mapsto [] :: [x] :: [\tau \mapsto []]}{[\tau \mapsto [] :: [\tau' \mapsto []]} L: [x] :=_{\tau} 1    L': [x] :=_{\tau$ | $[t \rightarrow t] = [t] + [t] + [t] = [t] + [t] = $ | - Par    |  |  |

| $\frac{[\tau \mapsto [] * \tau' \mapsto []] L^{r} [X] =_{\tau} 1    L^{r} [X] =_{\tau'} 2 [ok: (\tau \mapsto [e] * \tau' \mapsto [e']) \land \operatorname{race}(L, L', [e, e'])]}{[\tau \mapsto [] * \tau' \mapsto []] L^{r} [X] =_{\tau'} 2 [ok: (\tau \mapsto [e] * \tau' \mapsto [e']) \land \operatorname{race}(L, L', [e, e'])]} $ Cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |

At the last step of the derivation above, we apply the Construle of CISL to obtain race(L, L', [e, e']). Specifically, note that  $(\tau \mapsto [e] * \tau' \mapsto [e']) \land \text{race}(L, L', [e, e']) \Leftrightarrow \tau \mapsto [e] * \tau' \mapsto [e']$ , and we are only required to show that  $(\tau \mapsto [e] * \tau' \mapsto [e']) \land \text{race}(L, L', [e, e']) \Rightarrow \tau \mapsto [e] * \tau' \mapsto [e']$ .

**Duplicate Races.** Observe that using the same reasoning steps above, we can also derive race(L', L, [e', e]), identifying the same race between L and L' with a different witness history. However, duplicate race reporting can be avoided by simply inspecting the labels of racing instructions. For instance, once we report the race between L and L' via race(L, L', [e, e']), we can suppress all other witnesses of the form race(L, L', -) or race(L', L, -).

*Example 4.2 (Fig. 1f).* We present a proof outline of the race in Fig. 1f in Fig. 8, where we have annotated instructions with their thread identifiers and labels (where applicable). Note that we have encoded if  $(*) L'_{x}$ :  $[x] :=_{\tau_2} 1$  in the right thread using the non-deterministic choice (+) of CISL as  $L'_{x}$ :  $[x] :=_{\tau_2} 2 + \text{skip}$ . For brevity, rather than giving the full derivation, we follow the classical Hoare logic proof outline, annotating each line of the code with its pre- and post-condition. We further commentate each proof step and write e.g. // RD-LOCK to denote an application of RD-LOCK.

CISL<sub>RD</sub> Machine States (Par. 5) and Erasure (Par. 7). While a  $\text{CISL}_{\text{RD}}$  state  $s \in \text{STATE}_{\text{RD}}$  records the local (sequential) history associated with each thread, a  $CISL_{RD}$  machine state,  $m \in \text{MSTATE}_{\text{RD}}$  in Fig. 7, records the global execution history. A global history is obtained (through the  $\text{CISL}_{\text{RD}}$  erasure function) by combining all local thread histories into a well-formed history. That is, the  $CISL_{RD}$  erasure function is as defined below, where  $H|_{\tau}$  denotes restricting H to the events of  $\tau$ :  $\lfloor s \rfloor_{\text{RD}} \triangleq \{H \mid \forall \tau. s(\tau) = H' \Rightarrow H|_{\tau} = H'\}.$

**CISL**<sub>RD</sub> **Atomic Semantics (Par. 6).** The CISL<sub>RD</sub> atomic semantics is defined below, where each instruction of  $\tau$  extends the current history (machine state)  $H_g$  by inserting an associated event *e* in  $H_q$  such that *e* is the last event of  $\tau$  in the extended history, and the extended history is well-formed

(i.e. is in HIST). That is, whenever  $H_g$  can be split as  $H_\tau + H$  such that H does not contain any events associated with  $\tau$ , then executing an instruction associated with e may update  $H_g$  to  $H_\tau + e + H$ . Note that such splitting of  $H_g$  may not be unique; e.g. when  $H_g = [e_1 \cdots e_n]$  and none of  $e_1 \cdots e_n$  are associated with  $\tau$ , then  $R(L, \tau, x)$  may be inserted anywhere within  $H_g$ . Intuitively, this captures the different ways executing the instructions of one thread may be interleaved with those of others.

$$\begin{split} \llbracket \mathbf{L}: a :=_{\tau} \llbracket x \rrbracket_{A} ok &\triangleq \left\{ (H_{\tau} + H, H_{\tau} + e + H) \in \mathrm{HIST}^{2} \middle| e = \mathbb{R}(\mathbf{L}, \tau, x) \land \forall e' \in H. \ e'. \mathrm{tid} \neq \tau \right\} \\ \llbracket \mathbf{L}: \llbracket x \rrbracket_{\tau} =_{\tau} a \rrbracket_{A} ok &\triangleq \left\{ (H_{\tau} + H, H_{\tau} + e + H) \in \mathrm{HIST}^{2} \middle| e = \mathbb{W}(\mathbf{L}, \tau, x) \land \forall e' \in H. \ e'. \mathrm{tid} \neq \tau \right\} \\ \llbracket \mathrm{lock}_{\tau} \ l \rrbracket_{A} ok &\triangleq \left\{ (H_{\tau} + H, H_{\tau} + e + H) \in \mathrm{HIST}^{2} \middle| e = \mathbb{U}(\tau, l) \land \forall e' \in H. \ e'. \mathrm{tid} \neq \tau \right\} \\ \llbracket \mathrm{unlock}_{\tau} \ l \rrbracket_{A} ok &\triangleq \left\{ (H_{\tau} + H, H_{\tau} + e + H) \in \mathrm{HIST}^{2} \middle| e = \mathbb{U}(\tau, l) \land \forall e' \in H. \ e'. \mathrm{tid} \neq \tau \right\} \\ \end{split}$$

Note that the atomic semantics of  $lock_{\tau} l$  returns an empty set when the lock l is already held by  $\tau$ , thanks to the well-formedness condition on histories (see Fig. 7). Specifically, when the current machine state is  $H_1 = H_{\tau} + H$  (where H contains no actions by  $\tau$ ) and  $\tau$  then attempts to acquire the lock on l, then the resulting history  $H_2 = H_{\tau} + L(\tau, l) + H$  is well-formed and thus defined only if no other thread already holds the lock on l in  $H_{\tau}$ . That is,  $H_2$  is not well-formed (wf( $H_2$ ) does not hold) according to the definition in Fig. 7 when  $l \in alocks(H_{\tau}, \tau')$  for some  $\tau'$ . Consequently, when some thread  $\tau'$  already holds the lock on  $l, H_2$  is not defined, rendering the  $\{(H_1, H_2)\}$  set empty. Similarly, thanks to the well-formedness condition on histories, the atomic semantics of unlock  $\tau l$  returns an empty set when the lock l is not already held by  $\tau$ .

$CISL_{RD}$  Atomic Soundness (Par. 8). Finally, in the technical appendix [Raad et al. 2022] we demonstrate that the  $CISL_{RD}$  atomic instructions are sound.