# Flash: Fast, Consistent Data Plane Verification for Large-Scale Network Settings

Dong Guo Tongji University Shenshen Chen Tongji University Kai Gao Sichuan University

Qiao Xiang Xiamen University Ying Zhang Meta Inc. Y. Richard Yang Yale University

#### **ABSTRACT**

Data plane verification can be an important technique to reduce network disruptions, and researchers have recently made significant progress in achieving fast data plane verification. However, as we apply existing data plane verification techniques to large-scale networks, two problems appear due to extremes. First, existing techniques cannot handle too-fast arrivals, which we call *update storms*, when a large number of data plane updates must be processed in a short time. Second, existing techniques cannot handle well too-slow arrivals, which we call *long-tail update arrivals*, when the updates from a number of switches take a long time to arrive.

This paper presents Flash, a novel system that achieves fast, consistent data plane verification when update arrivals can include update storms, long-tail update arrivals, or both. In particular, Flash introduces a novel technique called *fast inverse model transformation* to swiftly transform a large block of rule updates to a block of *conflict-free updates* to efficiently handle update storms. Flash also introduces *consistent, efficient, early detection*, a systematic mechanism and associated novel algorithms to detect data plane violations with incomplete information, to avoid being delayed by long-tail arrivals. We fully implement Flash and conduct extensive evaluations under various settings. Using the data plane of a large-scale network, we show that compared with state-of-the-art sequential per-update verification systems, Flash is 9,000× faster.

# **CCS CONCEPTS**

• Networks  $\rightarrow$  Network reliability; Network monitoring; • Theory of computation  $\rightarrow$  Logic and verification.

#### **KEYWORDS**

Network Verification; Network Reliability; Network Monitoring

#### **ACM Reference Format:**

Dong Guo, Shenshen Chen, Kai Gao, Qiao Xiang, Ying Zhang, and Y. Richard Yang. 2022. Flash: Fast, Consistent Data Plane Verification for Large-Scale Network Settings. In ACM SIGCOMM 2022 Conference (SIGCOMM '22),

Dong Guo and Shenshen Chen contribute equally. Kai Gao and Qiao Xiang are co-corresponding authors.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

SIGCOMM '22, August 22–26, 2022, Amsterdam, Netherlands

© 2022 Association for Computing Machinery. ACM ISBN 978-1-4503-9420-8/22/08...\$15.00 https://doi.org/10.1145/3544216.3544246  $\label{eq:August 22-26, 2022, Amsterdam, Netherlands. ACM, New York, NY, USA, 22 pages. https://doi.org/10.1145/3544216.3544246$

#### 1 INTRODUCTION

Network faults such as forwarding loops, blackholes and access control violations are prevalent in large-scale computer networks, and can lead to disastrous financial and social consequences [1–3]. Thus, how to prevent network faults is a fundamental problem in the networking community.

A major advance is through network verification, which automatically checks network for errors in both control plane [4-14] and data plane [15-26]. In particular, we focus on the data plane verification in this paper, which checks the data plane and can find errors with a broad range of root causes.

There has been a long line of research on data plane verification [15–27]. Earlier tools develop verification algorithms on top of flow tables (*forward model*) (*e.g.*, [15, 17, 18, 27, 28]). Their performance is limited (*e.g.*, hundreds of milliseconds to seconds for a rule update) because flow table is not an efficient data representation for verification. As such, recent data plane verification tools introduce equivalent classes (*inverse model*) as the data representation for verification [21–26]. Although the number of equivalent classes can be exponential of network size, it is small in practice [21]. By developing efficient algorithms that transform the forward model to the inverse model, these tools achieve substantial speed up on verification. For example, the state-of-the-art APKeep [26] achieves a latency of tens of  $\mu s$  per rule update.

Motivated by the aforementioned advance, we start to construct a data plane verification tool, using the state-of-the-art, for a large production network, and evaluate the tool in a wide range of settings, including both online settings (e.g., fast monitoring [29, 30]), and offline settings (e.g., validation of FIBs derived from simulation [6, 31, 32]). The evaluations reveal that the state-of-the-art data plane verification techniques fall short in handling two problems, due to extremes which tend to appear in large-scale systems.

Handling Update Storms. First, existing techniques cannot handle too-fast data plane update arrivals, which we call *update storms*, when a large number of data plane updates should be processed in a short interval. Update storms can happen in both online settings and offline settings. In an online setting, for example, during a greenfield deployment or a major event (*e.g.*, disruption or recovery), a large number of switches can update their data planes, resulting in an aggregated large number of data plane updates (See Appendix A for examples). In an offline setting, state-of-the-art network simulation tools such as FastPlane [32] can compute the FIB of a network with more than 2,000 routers in a few hundreds of seconds, and the

scale of the RIB and FIB entries can be up to hundreds of millions. To conduct design searches, one may run simulations many times, and evaluate the result of each run quickly.

Designed to handle relatively smooth, limited-rate update arrivals, existing techniques process updates one-by-one and do not perform well. We have evaluated straightforward optimizations such as batch processing, in which multiple updates are sorted by switch, by IP address, or by operation type (e.g., add/delete). We have also applied divide-and-conquer [19] and partitioned a dataset of 6 million FIB updates in a Fabric topology with ~6,000 switches into 112 partitions, where each partition uses the state-of-the-art model-based data plane verifier [26], the system still takes tens of minutes to hours to complete the verification.

Handling Long-Tail Arrival. Second, existing mechanisms cannot handle too-slow arrivals, which we call *long-tail update arrivals*, when the updates from a number of switches can take a long time to arrive. Long-tail arrivals can happen for multiple reasons, such as FIB computation crashed or dampening [33], update packets loss due to incast congestion [34]. When update storms and long-tail arrivals happen together, the arrivals of data plane updates at the verification system may exhibit a bimodel pattern: an initial large update storm followed by additional updates that slowly trickle in from switches whose updates are delayed.

Existing data plane verification systems are designed with complete knowledge of the data plane, and hence they either wait until the full information is obtained, which can result in a long delay, or proceed with transient, potentially inconsistent information, which can result in false decisions. This issue is already reported by previous studies [7, 26], which use timeout as a compromise.

This paper presents Flash, a fast data plane verification system for networks where data plane updates can trigger update storms, long-tail update arrivals, or both. In particular, Flash contributes two new techniques to advance the state of the art on data plane verification: fast inverse model transformation (Fast IMT) to handle update storms, and consistent, efficient early detection (CE2D) to make fast, consistent decisions despite long-tail arrivals. Flash is a single system that integrates both techniques.

Fast IMT To Handle Update Storms (§3). We make a key observation that processing updates sequentially causes redundant or unnecessary computation and is inefficient when handling update storms. However, it is difficult to identify computation that can be aggregated across native rule updates, because a single rule update can be complex and result in a large number of operations. Fast IMT first uses an efficient, merge-based algorithm, to decompose a large block of native updates into a set of composable updates, which we call atomic conflict-free overwrites. It then applies two aggregation operators, first on actions, and then on predicates, to generate compact conflict-free overwrites, which are applied to update the inverse model. Given its similarity to the map-reduce framework, we call Fast IMT the novel map-reduce2 (MR2) algorithm. Combining MR2 with engineering efforts including subspace partition, fast look-up of overlapping rules, and persistent action tree, Fast IMT substantially reduces computation overhead for high scalability.

Consistent, Efficient, Early Detection to Handle Long-Tail Arrivals (§4). We make a key observation that network errors can be identified without collecting the complete data plane, and term

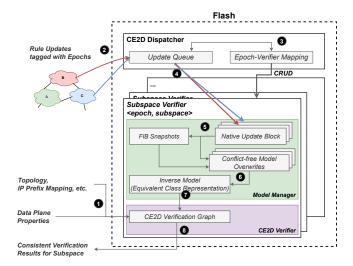

Figure 1: Architecture and workflow of Flash.

this process *early detection*. For example, a forwarding loop detected between two devices will exist regardless of how any other device forwards the packet. Therefore, this error can be reported without the FIB information of other devices, as long as the two devices are in a converged state (*i.e.*, not updating their FIB unless the network state changes). Flash is built on top of this observation, and introduces a systematic mechanism to ensure that Flash *always performs early detection on a consistent network state*. Specifically, Flash uses *epochs* to differentiate FIB updates computed from different network states, and applies early detection to the model constructed for *synchronized* devices in an epoch, *i.e.*, whose FIB is computed from the same network state. Flash captures the partial order of epochs for efficient scheduling. We then leverage automata theory to develop novel algorithms to achieve efficient early detection.

**Results (§5).** We implement Flash in this research and release it as an open-source software <sup>1</sup> (see details of the software in §5.1 and Appendix F). We conduct extensive evaluations of Flash with a wide range of topologies, data planes, update arrival patterns and policies. Using the data plane of a large-scale network (LNet), we show that Flash is  $9,000\times$  faster than state-of-art. Even if state-of-the-art tools integrate subspace partition, Flash is still over  $70\times$  faster. Flash achieves the preceding results by introducing both efficient algorithms (*i.e.*, Fast IMT and CE2D) and starting multiple verifiers in parallel. We also evaluate the computation overhead and operational cost of Flash, and show that the operational cost of Flash to verify a large-scale network (with >6,000 nodes and  $3.7\times10^7$  rules) can be as low as \$2.74/hour (\$24.016/year) for dedicated servers and \$4.352/hour (\$0.07/run) for on-demand one-shot verification.

This work does not raise any ethical issues.

#### 2 OVERVIEW

As introduced in §1, the ability of Flash to handle *update storms* and *long-tail arrivals* depends on two key novel techniques: *fast inverse model transformation* and *consistent, efficient early detection*.

<sup>&</sup>lt;sup>1</sup>https://github.com/snlab/flash

In this section, we give the architecture and workflow of Flash to illustrate how these techniques are combined into a single system, and leave the details in §3 and §4.

Figure 1 illustrates the architecture and workflow of Flash. There are two major components in the system.

**Subspace Verifier.** In a nutshell, a subspace verifier provides the same functionality as an ordinary data plane verifier: it receives FIB updates, reconstructs the data plane state, and verifies whether the properties are violated. In Flash, the subspace verifier is specialized for data plane verification tasks for large-scale networks. It consists of two parts: the *model manager* maintains a snapshot of the data plane based on the received FIB updates, and an equivalent class representation of the data plane computed using Fast IMT (§3); the *CE2D verifier* monitors the equivalent class representation and maintains a CE2D verification graph using consistent early detection algorithms in §4.

In Flash, each subspace verifier maintains the complete FIB snapshots but only verifies the properties for FIB snapshots of a specific *epoch* and a specific packet header subspace. While a subspace verifier can be configured to work as a standalone high-performance data plane verifier, it can only guarantee the correctness of consistent early detection by collaborating with CE2D dispatcher.

**CE2D Dispatcher.** The CE2D dispatcher has two responsibilities. First, it is responsible for managing the life cycles of subspace verifiers, i.e., creation, destruction, and reconfiguration. It also maintains a mapping from an epoch tag to the set of subspace verifiers who are responsible for verifying the properties for FIBs of the epoch. Second, the dispatcher is responsible for forwarding FIB updates to subspace verifiers based on the epoch-verifier mapping. Workflow. A typical workflow of using the Flash system is as illustrated in Figure 1. First, operators specify the verification requirements (1), i.e., data plane properties to be verified, using a specification language based on regular expressions. Static configurations such as the network topology and IP prefix mappings are also required to build the CE2D verification graph. After the system is up and running, it can receive FIB updates from routers, proxies or network simulators (2). To get consistent early detection results, these FIB updates should be tagged with an epoch tag.

Upon receiving a new epoch from a device (3), the CE2D dispatcher finds subspace verifiers whose epoch is outdated, stops their execution, and reconfigures them to verify the latest epoch, as specified §4.1. It then updates the epoch-verifier mapping and forwards FIB updates accordingly (4).

Each subspace verifier maintains an inverse model, *i.e.*, the equivalent class representation of the data plane. When a subspace verifier receives new FIB updates, it first dispatches them into blocks, which are used to compute the latest FIB snapshot and the conflict-free inverse model overwrites using Fast IMT in §3 (⑤). The conflict-free inverse model overwrites are then applied to obtain the latest inverse model that is consistent with the new FIB snapshot (⑥).

With the inverse model, the CE2D verifier updates the CE2D verification graph ( ) and applies the early detection algorithm. If a deterministic result is returned, the verifier returns a consistent verification results for the subspace ( ).

Table 1: Key Notations.

| Symbol               | Meaning                                                    |

|----------------------|------------------------------------------------------------|

| N                    | number of devices in a network                             |

| $\mathcal R$         | the rule-based representation of data plane $C$            |

| $r_{ik}, r$          | the $k$ -th rule in the $i$ -th device's FIB / a rule      |

| $m_{ik}, m_r$        | the match of $r_{ik}$ / $r$                                |

| $pri_{ik}$ , $pri_r$ | the priority of $r_{ik}$ / $r$                             |

| $a_{ik}, a_r$        | the actions of $r_{ik}$ / $r$                              |

| $e_{ik}, e_r$        | the effective predicate for $r_{ik}/r$                     |

| $p_i(y)$             | the predicate on the $i$ -th device when the action is $y$ |

| w                    | a conflict-free overwrite                                  |

| $a_w, p_w$           | the action/predicate of a conflict-free overwrite $u$      |

| M                    | the equivalent-class representation of data plane $C$      |

| $p^{j}$              | the predicate of the $j$ -th element in $M$                |

| $ec{ec{y}}^{j}$      | the action vector of the $j$ -th element in $M$            |

#### 3 FAST IMT

In this section, we give more details of Fast IMT. We first define the problem (§3.1), then give a high-level overview (§3.2), followed by the specification of the core merge-based block update decomposition algorithm (§3.3). More optimizations and data structures to improve speed and resource consumption in practice are given in (§3.4). See Table 1 for key notations.

# 3.1 Problem Definition and Background

A network data plane configuration C with N devices (routers or switches) can have two different representations that define the same forwarding behavior for any packet header h: the rule-based representation (forward model) and the equivalent class representation (inverse model).

**Rule-based Representation (Forward Model).** The rule-based representation of a network data plane is denoted as  $\mathcal{R} = \{R_i\}_N$ , where  $R_i$  denotes the forwarding table on the *i*-th device. A forwarding table consists of multiple forwarding rules in the format of  $\langle match, priority, action \rangle$  where the match field is a predicate (*i.e.*, a Boolean function on the packet header space), the priority field is an integer that specifies the priority of the rule, and the action is the action to be applied on the packets (e.g., forwarding, discarding).

Let  $r_{ik}$  denote the k-th rule in the i-th forwarding table, and let  $m_{ik}$ ,  $pri_{ik}$ , and  $a_{ik}$  denote the matching predicate, priority, and action of  $r_{ik}$  respectively. The forwarding behavior of C is a function<sup>2</sup>

$$\vec{b}_{\mathcal{R}}^{C}(h) = (b_1(h), \dots, b_N(h)),$$

where the action on the i-th device  $b_i(h)$  is determined by the rule of the highest priority that can match h:

$$b_i(h) = a_{ik^*}, \text{ where } k^* = \mathop{\arg\max}_{r_{ik} \in R_i, m_{ik}(h) = 1} pri_{ik}.$$

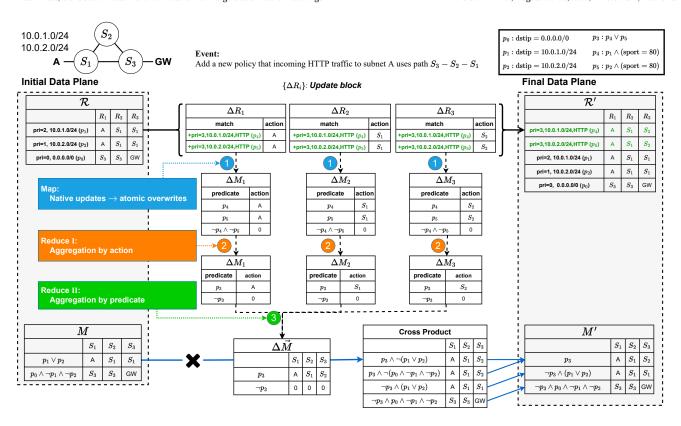

*Example (Rule-based Representation).* The table labelled  $\mathcal{R}$  on the upper left corner of Figure 2 is an example of the FIBs (rule-based representation) of the 3-node network above the table. For compact figure, we show the FIBs of the 3 switches in 3 columns (*i.e.*,  $R_i$  is for switch  $S_i$ ). For simplicity, we assume that the rules are forwarding rules and use their next hop as the action, and that the rules are

$<sup>^2</sup>$  This requires that a data plane configuration C does not have syntax errors caused by ambiguous or conflicting forwarding rules, *i.e.*, two rules with overlapping match, same priority but conflicting actions. This typically indicates an error or can be resolved using prior work such as FlowVisor [35].

numbered by the row number. To illustrate how to read the table, consider an example packet header  $h_1$  whose destination IP address is 10.0.1.2. At  $S_1$  (using  $R_1$ ), both rule  $r_{11}$  ( $\langle dip = 10.0.1.0/24, 2, A \rangle$ ) and rule  $r_{13}$  ( $\langle dip = 0.0.0.0/0, 0, S_3 \rangle$ ) in  $R_1$  can match it, but rule  $r_{11}$  has a higher priority. Thus, the output of  $b_1(h)$  is A. Looking up  $h_1$  on  $S_2$  (using  $R_2$ ) and on  $S_3$  (using  $R_3$ ) with the same procedure, the final output is a vector:  $b_R^C(h_1) = (A, S_1, S_1)$ .

**Equivalent Class Representation (Inverse Model).** The equivalent class representation of a network data plane is denoted as  $M = \{(p^j, \vec{y}^j)\}_j$ , where  $(p^j, \vec{y}^j)$  denote the j-th element in M.  $\forall j$ ,  $p^j$  is a predicate and  $\vec{y}^j$  is an N-dimension action vector, where  $y_i^j$  specifies the action on the i-th device. In a valid equivalent class representation M, the entries are 1) unique:  $\forall j \neq j', \vec{y}^j \neq \vec{y}^{j'}$ ; 2) unitually exclusive:  $\forall j \neq j', \forall h, p^j(h) \land p^j(h) = 0$ ; and 3) complementary:  $\forall h, \exists j, p^j(h) = 1$ . Given the characteristics of  $p^j$ , they represent atomic predicates originally developed in [21].

In the equivalent class representation, the forwarding behavior of C can be expressed as a function

$$\vec{b}_{M}^{C}(h) = \vec{y}^{j^{*}}$$

, where  $p^{j^{*}}(h) = 1$ .

**Inverse Model Transformation.** While the network uses the forward model (rule-based representation), the inverse model (equivalent class representation), on the other hand, provides an efficient data structure for use cases such that given the forwarding behavior  $\vec{y}^j$ , find the header spaces  $p^j$ . In general, a data plane verifier checks whether an unacceptable  $\vec{y}^j$  exists. Hence, the goal of data plane verification is to transform the forward model  $\mathcal R$  to the inverse model  $\mathcal R$ , and  $\mathcal R$  is equivalent with  $\mathcal R$ , denoted as  $\mathcal R \sim \mathcal M$ , which is defined as, if and only if  $\forall h, \vec{b}^C_{\mathcal R}(h) = \vec{b}^C_M(h)$ .

Example (Equivalent Class Representation). The table labelled M on the lower left corner of Figure 2 is the inverse model of  $\mathcal{R}$ . One can observe that the network has 2 behaviors:  $(A, S_1, S_1)$  for those packet headers in  $p_1 \vee p_2$ , and  $(S_3, S_3, GW)$  for the rest. A data plane verifier typically builds a graph data structure to represent the vectors and runs graph algorithms to check properties on the graph (e.g., no loop). The execution time of the graph algorithms typically is negligible compared with the time to construct M.

**Rule Updates and Inverse Model Updates.** Upon updates in the data plane such as rule insertions, deletions or modifications, the rule-based representation transfers from the initial state  $\mathcal{R}$  to the final state  $\mathcal{R}'$ . Accordingly, the equivalence-class model must also transfer from the initial state M to a final state M' where  $\mathcal{R}' \sim M'$ . The right hand side of Figure 2 shows an example of the updated models of the network, when rules are inserted in the 3 switches to handle HTTP to the two subnets specially.

The preceding is a generalization of the computation process of global atomic predicates [21] and APKeep [26]: the global AP is solving the special case where there are no initial rules, *i.e.*,  $\mathcal{R} = (\emptyset, \dots, \emptyset)$ , while the APKeep work is solving the special case where each update has only one rule.

# 3.2 Fast IMT Intuition

With the precise problem definition, we now give the design of Fast IMT. Instead of giving the algorithm bottom up, we focus on building intuitions in this section. A formal, bottom-up model of Fast IMT and its correctness is in Appendix C.

**Intuition I: Direct Transformation Revealing Native Update Complexity.** First consider direct transformation, which is computationally inefficient but gives us intuition on computing the effect of an update in the forward model. In particular, consider how to compute the predicate  $p^j$  for  $\vec{y}^j$ , for each equivalent class  $(p^j, \vec{y}^j)$ . Let  $p_i(a)$  denote the predicate that selects the header spaces for which the i-th device takes action a. Then  $p_i(y_i^j)$  is the union of the *effective predicate* of each rule  $r_{ik}$ , whose action  $a_{ik}$  is  $y_i^j$ , and the *effective predicate*  $e_{ik}$  of rule  $r_{ik}$  1) satisfies the match condition of  $r_{ik}$ , and 2) is not matched by a rule with a higher priority, i.e.,

$$e_{ik} = m_{ik} \land \neg \bigvee_{pri_{ik'} > pri_{ik}} m_{ik'}. \tag{1}$$

For the header space to take  $\vec{y}^j$ , the predicate  $p^j$  must satisfy all  $p_i(y_i^j)$ , *i.e.*, by taking their conjunction:

$$p^{j} = \bigwedge_{\forall i} p_{i}(y_{i}^{j}) = \bigwedge_{\forall i} \left( \bigvee_{a_{ik} = y_{i}^{j}} e_{ik} \right). \tag{2}$$

Equations (1) and (2) show that the effects of a native update (*i.e.*, an update in the forward model) can be global and quite complex in the inverse model. The insertion of a new rule can reduce the effective predicates of a large number of rules with lower priorities, and these rules can have different actions. Meanwhile, the deletion of a rule can increase the effective predicates of a large number of rules with lower priorities, and these rules can also have different actions. In both cases, multiple  $p^j$  s may need to be updated.

**Intuition II: Per-Rule Updates Can be Inefficient.** We now build intuition on that per-rule updates are inefficient. Consider two rules  $r_1$  and  $r_2$  with  $k_1$  and  $k_2$  ( $k_1 < k_2$ ) rules that have a higher priority on the same device. To compute the effective predicates for  $r_1$  and  $r_2$ , they need to visit  $k_1$  and  $k_2$  rules. However, as  $k_1 < k_2$ , computing the union of the first  $k_1$  rules when processing  $r_2$  is redundant, which is already computed when processing  $r_1$ . Upon an update storm, the redundancy can be quite substantial.

Such redundancy also exists when updating the  $p^j$ s. To be concrete, consider the updates in Figure 2, which install 6 new rules, with 2 new rules in each switch shown in the top middle of the figure. A simple approach to update the inverse model is to apply the 6 updates one by one. On the other hand, one can verify from the example that clearly the 6 updates can be combined and applied together. Specifically, the 6 updates have only two distinct match conditions ( $p_4$  and  $p_5$ ). At the final inverse model shown in the lower right corner,  $p_4$  and  $p_5$  do not appear individually, but appear only as the union  $p_3 = p_4 \vee p_5$ .

**Intuition III: Overwrite Operators Allowing Update Composition**. To understand the essence why the updates can be combined, consider the first update at  $S_3$  (first row of  $\Delta R_3$  in Figure 2), as an *inverse model overwrite* operator (or *overwrite* for short):  $(\Delta p = p_4, \Delta y)$ , where  $\Delta y$  specifies that it sets the action at  $S_3$  to  $S_2$ , written as  $\{y_3 = S_2\}$ . The effect of the operator is that for each equivalent class  $(p^j, \vec{y}^j)$ , if the intersection  $p^j \wedge \Delta p$  is empty, the operator has no effect; otherwise, the intersected header space should be moved to the other equivalent class with device  $S_3$  taking action  $S_2$  and the rest of  $\vec{y}^j$  not changed. The computation process is similar to database *join* and we refer to it as a *cross product*.

Figure 2: A simple example illustrating Fast IMT.

Now consider the second rule insertion  $(p_5, S_2)$ ,  $\Delta y$  and the process are the same except that  $\Delta p = p_5$ . If we use  $(\Delta p = p_4 \lor p_5, \Delta y)$ , the two processes can be composed, improving efficiency.

Next consider the relationship between two overwrites at two switches: the first update  $(p_4, \{y_1 = A\})$  at  $S_2$  and the first at  $S_3$   $(p_4, \{y_2 = S_1\})$ . One can see that they have the same predicate  $(p_4)$ . We observe that this happens frequently, as often an update is to set up a new network-wide flow, and the predicate selects the same flow. Still using the overwrite operator perspective, we can compose the two updates into a single one  $(\Delta p = p_4, \Delta y)$ , where  $\Delta y$  is  $\{y_2 = S_1, y_3 = S_2\}$ .

Both examples can be considered as applying a "reduce" operator in the map-reduce framework [36]. In the first "reduce", the key is  $\Delta y$ , and the predicates  $(\Delta p)$  are reduced (by predicate disjunction), for those with the same key. In the second "reduce", the key is  $\Delta p$ , and the updates  $(\Delta y)$  are reduced (by combining function effects). Figure 2 illustrates these two "reduce" operators, shown as Reduce I and Reduce II, respectively. One need to note that the "reduce" operators guarantee the *conflict-free property*. We say that two overwrite operators  $(\Delta p, \Delta y)$  and  $(\Delta p', \Delta y')$  have a conflict, if only if  $\Delta p$  and  $\Delta p'$  intersect, and they write different actions at the same device but with different actions.

Note that the preceding "map-reduce" process applies only to conflict-free overwrite operators. As we discuss in Intuition I, a native rule update can be complex and is not a conflict-free overwrite. The remaining key idea of Fast IMT is to turn native rule

updates into conflict-free overwrites<sup>3</sup>, which we show in the next subsection. In particular, if an overwrite only changes the action of a single device, we call it an *atomic overwrite*, and we denote the set of atomic overwrite operators for device i as  $\Delta M_i$ . This process can be considered as a "map" operation in map-reduce, where each native rule update for device i is mapped to a set of atomic overwrites. Since Fast IMT can be considered a "map" followed by two "reduce", we also refer to it as the MR2 algorithm.

### 3.3 Efficiently Computing $\Delta M_i$

Given an update block with K updates for a flow table  $R_i$  with T entries, a naive, sequential algorithm can compute  $\Delta M_i$  in O(KT) complexity. This, however, is inefficient. We apply the list merge idea and design Algorithm 1, which consists of two phases: merging the native updates in the block and finding expanding rules (L3), and then computing atomic overwrites for the expanding rules (L5).

**Merging Native Updates.** The merging (L7-28) is similar to merging two sorted list, where r and  $\delta$  represent the heads of  $R_i$  and  $\Delta R_i$  respectively<sup>4</sup>. A Boolean variable is used to indicate whether a rule with higher priority is deleted, which means the effective predicate of the current rule r may expand. The algorithm iterates through the updates (L12-25). It first locates where the update should be

<sup>&</sup>lt;sup>3</sup>We use "overwrite" to refer to "conflict-free overwrite" in the rest of the paper, as long as there is no ambiguity.

<sup>&</sup>lt;sup>4</sup>Note that with the default wildcard rule with the lowest priority, r will never reach the end of  $R_i$  so no check on r is needed. The same observation applies to CalculateAtomicOverwrite( $R_i'$ ,  $R_{diff}$ ) as well.

**Algorithm 1:** Decomposing Native Rule Update Blocks into Atomic Overwrites through Merging.

```

Input

: \Delta R_i - the block of native updates on the i-th device

Input : R_i - the sorted initial rule set before the update Output : R'_i - the sorted final rule set after the update

Output : \Delta M_i - the set of atomic overwrites that is equivalent to \Delta R_i

1 \Delta R_i ← remove canceling updates in \Delta R_i

// (insert-after-delete or delete-after-insert)

2 \Delta R_i ← sort \Delta R_i by priority in the descending order

3 R_{diff} \leftarrow \text{MergeBlockAndDiff}(R_i, \Delta R_i)

4 R'_i \leftarrow R_i // updates have been applied to R_i

5 \Delta M_i \leftarrow \text{CalculateAtomicOverwrite}(R'_i, R_{diff})

return R'_i, \Delta M_i

Function MergeBlockAndDiff(R_i, \Delta R_i)

R_{diff} \leftarrow \text{empty list}

higher\_priority\_rule\_deleted \leftarrow \mathbf{false}

\leftarrow the rule with the highest priority in R_i

\delta = (op, r_{\delta}) \leftarrow the update with the highest priority in \Delta R_i

11

while \delta \neq NULL do

12

if r_{\delta} is inserted/deleted after r then

\begin{array}{c} \textbf{if } \textit{higher\_priority\_rule\_deleted } \textbf{then} \\ & \bot \textbf{Append } r \textbf{ to } R_{\textit{diff}} \textit{ // } r \textbf{ may expand} \end{array}

14

15

r \leftarrow \text{get the next rule in } R_i

16

17

else

if op is insertion then

18

Insert r_{\delta} before r // rule insertion

19

Append r to R_{\it diff} // New rules expand

20

else if op is a deletion (r_{\delta} = r) then

21

Delete r from R_i // rule deletion

22

higher\_priority\_rule\_deleted \leftarrow true

23

r \leftarrow \text{get the next rule in } R_i

24

\delta \leftarrow get the next update in \Delta R_i

25

if higher_priority_rule_deleted then

Append remaining rules in R_i to R_{diff}

27

28

return R_{diff}

Function CALCULATEATOMICOVERWRITE(R'_i, R_{diff})

29

\Delta M_i \leftarrow \emptyset

30

r \leftarrow the rule with the highest priority in R'_i

31

r_{\delta} \leftarrow the rule with the highest priority in R_{diff}

p \leftarrow 0 \, / / accumulative predicate (\bigvee_{\texttt{pri}_{ik'} > \texttt{pri}_{ik}} m_{ik'})

33

← 1 // predicate of "no-overwrite" action

while r_{\delta} \neq NULL do

while r_{\delta} has a lower/equal priority than r and r \neq r_{\delta} do

p \leftarrow p \vee m_r

37

38

r \leftarrow \text{get the next rule in } R'_i

\mathit{eff} \leftarrow m_{r_{\mathcal{S}}} \land \lnot p \mathrel{//} \mathsf{effective} \; \mathsf{predicate} \; \mathsf{of} \; r_{\mathcal{S}}

39

\Delta M_i \leftarrow \Delta M_i \cup \{(\mathit{eff}, \{y_i = a_{r_{\delta}}\})\}

40

41

p_c \leftarrow p_c \land \neg eff

r_{\delta} \leftarrow \text{get the next rule in } R_{diff}

42

\Delta M_i \leftarrow \Delta M_i \cup \{(p_c, \emptyset)\}

return \Delta M_i

```

applied (L13-16). For an insertion update (L18-20),  $r_{\delta}$  should be inserted before r and the new rule  $r_{\delta}$  is also expanding. For a rule deletion (L21-24),  $r=r_{\delta}$  and should be deleted. In the meantime, rules with a lower priority in  $R_i$  may expand (L14-15, L26-27) so the indicator is updated (L23). For K rule updates in a table with T rules, this step takes  $O(K \lg K + T)$  simple operations.

**Computing Atomic Overwrites.** To compute atomic overwrites, a critical step is to compute the effective predicates of each expanding rule. Flash uses the property that both  $R'_i$  and  $R_{diff}$  are sorted. The procedure is in L29-44. First, r and  $r_{\delta}$  are set to the head of R' and  $R_{diff}$  respectively. The algorithm iterates through  $R_{diff}$  (L35-42). First, it locates where  $r_{\delta}$  is in  $R'_i$ . The predicate p is the union of all rules that have a higher priority than  $r_{\delta}$  (L37), and the effective

predicate of  $r_{\delta}$ , eff, is computed in L39. Then an atomic overwrite  $(eff, \{y_i = a_{r_{\delta}}\})$  is added to  $\Delta M_i$  (L40). The *complementary predicate* is the predicate for the special "no-update" overwrite, and it is maintained by subtracting the predicates of overwrites with a concrete action (L41). This step takes O(T+K) predicate operations as each rule is visited only once.

Thus, the algorithm takes  $O(K \lg K + T)$  simple operations and O(T + K) predicate operations, *i.e.*, conjunction ( $\land$ ), disjunction ( $\lor$ ), or negation ( $\lnot$ ), in the worst case. In practice, T > K and predicate operations are much more expensive than a simple operation. Thus, Algorithm 1 is much faster compared to per-update processing, which takes O(KT) simple and predicate operations.

#### 3.4 Fast IMT in Action

While Fast IMT has reduced substantially amount of redundant computation for a large number of updates, there are still engineering optimizations that can be adopted to further improve the speed and resource consumption.

Input Space Partition. The complexity of Fast IMT depends on the sizes of the inverse model and the updates, which are both related to the number of rules in the data plane. By partitioning the space into multiple subspaces, the number of valid pairs in the update process can be reduced, as well as the number of affected rules. Thus, it can substantially improve the speed of model update. Fast Look-up for Overlapped Rules. The key step in computing atomic overwrites  $(\Delta M_i)$  is to calculate the effective predicate of each affected rule. One can see that the effective predicate of a rule r will affect or be affected by another rule r' only if their matches overlap, i.e.,  $m_r \wedge m_{r'} \neq \emptyset$ . In some common scenarios, for example, when the data plane mainly consists of longest prefix matching rules, the number of overlapped rules is usually much smaller than the number of rules on a device. To speed up the computation of atomic overwrites, Flash uses a multi-dimension prefix Trie [24] to enable fast look-up for overlapped rules.

**Persistent Action Tree.** A common operation is to compute the new actions  $\vec{y}^*$  by overwriting some elements in the old actions  $\vec{y}$ . A naive solution, *e.g.*, storing the vector as an array, may take linear time and units. However, the overwriting process of multiple output vectors may have the same sub output vector. Let  $\|\vec{y}\|_{\neq 0}$  denote the number of non-zero elements in  $\vec{y}$ . In the overwriting process,  $\vec{y}$  is from M and  $\|\vec{y}\|_{\neq 0}$  is usually large. In contrast,  $\|\vec{y}^*\|_{\neq 0}$  often equals to one. In Flash, a data structure called persistent action tree (PAT) is introduced. PAT is a persistent [37] balanced binary search tree, which only creates a chain until each node is modified by  $\vec{y}^*$ . Thus, a single overwriting takes at most  $O(\|\vec{y}^*\|_{\neq 0} \times \lg \|\vec{y}\|_{\neq 0})$  time instead of  $O(\|\vec{y}^*\|_{\neq 0} + \|\vec{y}\|_{\neq 0})$ .

# 4 CONSISTENT, EFFICIENT EARLY DETECTION

In this section, we introduce how Flash systematically achieves consistent, efficient, early detection. The motivation of consistent early detection comes from the following observation: logically centralized data plane verifiers like Flash need to collect FIB updates either from a centralized database (as in SDN) or from distributed devices, while large-scale networks today use distributed protocols. Existing verifiers require complete knowledge of the data plane,

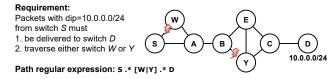

Figure 3: An example of network update setting.

which may take a long time to arrive or even trigger out-of-order deliveries. If the verifier waits until it receives all the updates, it may suffer from intolerable delays or even become unavailable. However, if a verifier simply applies all updates to a single model, it may either report a transient error or even wrong results.

Specifically, Flash proposes solutions to the following two key problems: (1) How to dispatch the rule updates to construct models that are consistent with the converged state? (2) How to efficiently compute verification results with incomplete information? We refer to our solutions as *consistent model construction* and *efficient early detection* (CE2D), respectively.

#### 4.1 Consistent Model Construction

To achieve consistent model construction, Flash must (1) identify consistent FIB updates, *i.e.*, those that are computed from the same network state; (2) identify *potential* converged states; (3) dispatch consistent FIB updates (for *correctness*) of a potential converged state (for *efficiency*) to the same verifier<sup>5</sup>. We have designed mechanisms to construct consistent models for multiple routing protocols. Below, we focus on broadcast state synchronization protocols (or sync-state protocols for short), including link-state protocol OSPF/I-SIS and general state synchronization protocol OpenR. We discuss vector-based protocols (*e.g.*, BGP) in Appendix D.1.

**Identifying Consistent FIB Updates with Epoch.** Flash uses *network state* to denote the information which is used by routing software to compute the forwarding rules (*e.g.*, link states and prefix configuration). As a network is evolving, its state also changes triggered by different events (*e.g.*, link failure). In sync-state protocols, the state changes are propagated to the entire network.

Flash differentiates the rule updates computed from different network states by dividing them into *epochs*. Specifically, each epoch represents a snapshot of the global network state. As it is not possible to determine whether updates are from the same network state by only looking at the data plane, Flash augments the routing software with an agent. The agent computes the  $tag^6$ , a unique identifier of an epoch, and associates the tag with FIB updates computed from the state. Flash requires that the message delivery between the agent and the dispatcher is serialized, *i.e.*, updates from the same device are always received in the same order as they are generated. However, Flash does not have any constraints on messages from agents on different devices.

**Identifying Potential Converged State through Epoch Dependency Tracking.** As Flash requires a strict order between a device and the dispatcher, if the dispatcher receives updates with  $t_1$  on device i before receiving those with  $t_2$ ,  $t_1$  cannot be the converged state. Similarly, if we see  $t_2$  before  $t_3$  on device j, even if  $t_2$  is the most recent tag on device i, we can infer that  $t_2$  cannot be the converged state. This is referred to as the "happens-before" relation in distributed systems, denoted as  $t_1 < t_2$ . Flash maintains the most recent tag for each device and a set of "active" epochs which has no succeeding epochs. Once a new tag  $t_{\rm new}$  is received from device i, whose old tag is  $t_i = t_{\rm old}$ , Flash removes  $t_{\rm old}$  from the active set and replaces  $t_i$  with  $t_{\rm new}$ . If  $t_{\rm new}$  is not marked as inactive (by another device), Flash adds  $t_{\rm new}$  to the active set. An epoch, whose tag is in the active set, is a potential converged state.

**Dispatching Consistent FIB Updates** As the updates are associated with epoch tags, Flash maintains a mapping from an epoch tag to a verifier. Specifically, upon receiving updates with a new epoch tag t from a device, Flash first appends the updates to the update queue of the device, and checks whether t is in the active set. If t is not in the active set, which means there will be future updates on the same device, no further action is required. Otherwise, if t is in the active set, Flash finds (or creates one if not present) the verifier for t, and feeds the updates from the device's update queue to that verifier. In practice, Flash may need to adopt a back-off mechanism to avoid rapid creation of verifiers due to control plane bugs or improper handling of unstable links.

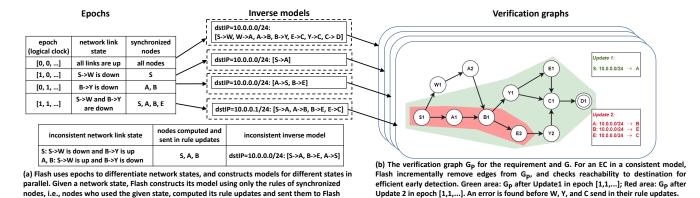

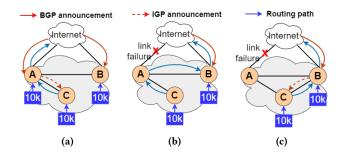

An example update setting is as shown in Figure 3. Consider the updates triggered by two link failures: (S, W) and (B, Y). Assume the initial tag is  $t_0 = [0, 0, ...]^7$  for each device, where the first/second element is the version of link (S, W)/(B, Y). Assume that at time  $T_1$ , Flash receives updates from S with tag  $t_1 = [1, 0, ...]$  (after seeing the failure of (S, W)), and from switches A and B with tag  $t_2 = [0, 1, ...]$  (after seeing failure of (B, Y)). At  $T_1$ ,  $t_1$  and  $t_2$ are potential converged states and are put in different verifiers8. However, if at time  $T_2 > T_1$ , Flash receives updates from switch S, A and B with epoch tag  $t_3 = [1, 1, ...]$ , the dispatcher will mark  $t_1$  and  $t_2$  as inactive, and creates a new verifier for  $t_3$  as  $t_3$  is now active. Then, if Flash receives updates tagged with  $t_2$  from switch E, Flash simply appends the updates to the queue of E, and does not dispatch them to any verifier. When it receives updates with t<sub>3</sub> from E, it flushes the updates to the verifier associated with tag t3. Figure 4 (a) shows the models constructed for each epoch and shows an example of an inconsistent state at the bottom.

# 4.2 Consistent Early Detection for General Regular Expression Requirements

We first specify how Flash performs consistent early detection for general requirements specified in regular expressions (see Appendix B for detail), including waypoint routing, shortest path, anycast, and multicast, etc. Specifically, Flash leverages the automata theory [40] to transform this problem into an incremental reachability query problem on a decremental verification graph [41].

<sup>&</sup>lt;sup>5</sup>Note that it is not a hard constraint to only run verifiers for converged states, which can be useful when trying to locate the source of an error. However, it can reduce the resource overhead when the network operators are only interested in the verification result of potentially converged state.

<sup>&</sup>lt;sup>6</sup>In our OpenR implementation, Flash uses the hash value of the keys and versions of the state variables as the epoch tag. We use an XOR based hash function in Boost [38] that can compute the hash value of 1 million entries within 10ms on commodity switches (e.g., Barefoot S9180-32X [39]). To reduce the probability of hash collision, Flash may use multiple hash functions and concatenate the results.

$<sup>^7\</sup>mathrm{To}$  better illustrate the partial happens-before relationship between epochs, we use the logical clock vector as the tag only in this example.

<sup>&</sup>lt;sup>8</sup>Note that with a logical clock vector, one may even conclude that both  $t_1$  and  $t_2$  will not be the converged state. However, in practice, it may not be able to derive the causal relationship with the "happens-before" observations.

Figure 4: An illustration to consistent, efficient early detection for the update setting in Figure 3.

**Verification Graph and Consistent Partial Verification.** Flash computes the verification graph [40, 42–44] as the cross product automata  $G_p$  of the network automata and the requirement expression automata, for each packet space H and a set of sources srcs. The initial verification graph contains all paths in G that (1) start from srcs, and (2) match all the regular expressions.

Consider the network and requirement in Figure 3. The requirement is that packets in subspace h that enters at S must reach D along a simple path traversing one of W and Y. Figure 4(b) shows the verification graph with initial state S1 and accepting state D1.

With this graph, verification of the requirement expression is equivalent to finding a path that can reach an accept state in the verification graph. Specifically, if there exists such a path consisting of only synchronized nodes, the requirement is consistently satisfied. And if there exists a path consisting of only synchronized nodes to the reject state, the requirement is consistently unsatisfied. Otherwise, the verification result is *unknown*.

**Decremental Update and Reachability Query.** With more nodes becoming synchronized, the set of possible requirement-compliant paths in the network for this epoch are monotonically decreasing. Consider the example in Figure 3, after receiving *Update 1* as in Figure 4(b), the verification graph only contains the nodes and edges in the green area. After further receiving *Update 2*, no valid path is in  $G_P$ , which means the requirement in Figure 3 cannot be satisfied, no matter how h is forwarded by other devices. The reachability query in such a decremental graph (*i.e.*, edges are always removed, but never added) has a constant time complexity [41]. The details and pseudocode of the algorithm, as well as how it is extended to perform early detection for more complex traffic patterns (*e.g.*, anycast, multicast, and coverage requirements [27]), is in Appendix D.2.

# 4.3 Consistent Early Loop Detection

Loop detection is a basic task. However, expressing loop detection requires complex regular expressions and hence is not efficient. Thus, we design a specific CE2D algorithm to check loop(s). A naive approach is to delete unsynchronized nodes and then check if there is a loop in the synchronized nodes, which is simple but can miss early detection opportunities. An alternative is to keep the unsynchronized nodes but assume that an unsynchronized node can take any potential next hop, and the system enumerates all

(a) C and X are unsynchronized.

(b) X is unsynchronized.

Figure 5: Examples of all-pair loop-detection.

combinations, which can be computationally expensive. Flash combines the best of these two approaches by introducing a technique called *hyper node compression*.

**Hyper Node Compression.** Each connected component of unsynchronized nodes is compressed as a hyper node to reduce the cost of enumeration. Let U denote a connected component of unsynchronized nodes, which is replaced by a hyper node w. For each  $(u,v) \in E$ ,  $u \notin U$  and  $v \in U$ , remove (u,v) and add an edge (u,w) to E. Verifying this graph with hyper nodes will give the same result as the second approach, but avoids the enumeration of paths in U.

Consider the example in Figure 5. In Figure 5(a), when  $sync = \{A, B\}$ , we can merge unsynchronized nodes C and X into a hyper node, denoted as C&X. In this case, there can potentially be a loop, e.g.,  $B \rightarrow A \rightarrow C\&X \rightarrow B$ , which is  $B \rightarrow A \rightarrow X \rightarrow B$  in the original graph, or be no loop, e.g.,  $B \rightarrow A \rightarrow C\&X \rightarrow out$ , which is  $B \rightarrow A \rightarrow X \rightarrow C \rightarrow out$ . Thus, the final result is not determined. However, if C is synchronized, as in Figure 5(b), Flash reports that as long as X does not drop the packet  $^9$ , there will be a loop in the final state. This cannot be detected if only synchronized nodes are verified.

**Incremental Detection.** Instead of detecting loops from all possible nodes, Flash only detects loops that contain the nodes that just become synchronized. Let  $V_S$  and  $V_S'$  denote the old and new set of synchronized nodes accordingly. If no loop is detected in the old graph, a new loop in the new graph must contain a node in  $V_S' \setminus V_S$ . Combining hyper node abstraction and incremental detection, Flash incrementally examines new synchronized nodes. If a loop composed of only synchronized nodes is found, the error is reported. Details of the algorithm are given in Appendix D.3.

<sup>&</sup>lt;sup>9</sup>In certain cases such as ACL, dropping packets is considered acceptable. This algorithm only needs a small revision to work in that case, *i.e.*, making explicit "DROP" action as forwarding to a "virtual switch".

| Setting                         | Topology  |                   | FIB Generation                                                                            | FIB Scale                                 | Update Generation                                                                                                                  | Update Scale                              | Arrival Pattern                                                                                                                     |  |

|---------------------------------|-----------|-------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| g                               | Name      | V / E             |                                                                                           |                                           | op and of an and an                                                                            | · F                                       |                                                                                                                                     |  |

| LNet-apsp Subspace<br>LNet-apsp | LNet      | 6,016 /<br>43,008 | StdFIB: Shortest path<br>from each node to the<br>hosts connected to the<br>rack switches | $\frac{2.9 \times 10^5}{3.2 \times 10^7}$ | Insert each rule in a sequence and then delete it                                                                                  | $\frac{5.8 \times 10^5}{6.4 \times 10^7}$ | Updates burst into the                                                                                                              |  |

| LNet-ecmp Subspace LNet-ecmp    |           |                   | StdFIB*: StdFIB with<br>source match ECMP                                                 | $\frac{3.0 \times 10^5}{3.7 \times 10^7}$ | in the same order from the sequence                                                                                                | $\frac{6.0 \times 10^6}{7.4 \times 10^7}$ | verifier                                                                                                                            |  |

| LNet-smr Subspace<br>LNet-smr   |           |                   | StdFIB* with suffix match routing                                                         | $\frac{2.6 \times 10^6}{3.7 \times 10^7}$ |                                                                                                                                    | $\frac{5.2 \times 10^6}{7.4 \times 10^7}$ |                                                                                                                                     |  |

| Airtel-trace                    | Airtel 1  | 68 / 260          | Extracted from dataset                                                                    | 6.89 × 10 <sup>4</sup>                    | Extracted from dataset (as a single sequence) $1.42 \times 10$                                                                     |                                           |                                                                                                                                     |  |

| Stanford-trace                  | Stanford  | 16 / 37           |                                                                                           | $3.84 \times 10^{3}$                      | Same as LNet-apsp                                                                                                                  | $7.68 \times 10^{3}$                      |                                                                                                                                     |  |

| I2-trace                        |           |                   |                                                                                           | $1.26 \times 10^{5}$                      |                                                                                                                                    | $2.25 \times 10^{5}$                      |                                                                                                                                     |  |

| I2-OpenR-loop                   | Internet2 | 9 / 28            | Generated by correct<br>OpenR software                                                    | 216                                       | Each OpenR switch<br>computes the correct FIB<br>updates upon receiving<br>state syncing messages<br>from link events              | Dynamic                                   | Updates are sent to the<br>verifier according to the<br>reaction of real OpenR<br>software under link<br>events                     |  |

| I2-OpenR/1buggy-loop-lt         |           |                   | Generated by buggy<br>OpenR software                                                      |                                           | Same as the I2-OpenR-loop<br>setting, with one switch<br>running a buggy OpenR<br>software that generates<br>incorrect FIB updates |                                           | Same as the I2-OpenR-loop<br>setting with one or more<br>switches are configured<br>with an init/max 60s FIB<br>computation backoff |  |

| I2-trace-loop-lt                |           |                   | Extracted from dataset                                                                    | $1.26 \times 10^{5}$                      | Extracted from dataset                                                                                                             | $<1.26 \times 10^{5}$                     |                                                                                                                                     |  |

Table 2: Settings used in the evaluation.

### **5 EVALUATION**

We fully implement Flash and conduct extensive evaluations using various settings, including a real data plane sampled from a large network (LNet), to answer key questions including but not limited to the following: (1) What is the performance of Flash in a real-world, large-scale network with a large number of updates? How robust is the performance of Flash under different settings? (§5.2) (2) What is the performance of Flash with the arrival pattern of FIB updates from real routing suits? (§5.3) (3) How does each optimization technique contribute to the overall performance improvement? (§5.4) (4) What is the overhead (cost) of Flash in terms of computational demand? (§5.5)

#### 5.1 Methodology

Settings. The performance of network verification depends on multiple factors, including topology, FIB pattern, FIB update arrival pattern, and the requirements. For Fast IMT, the settings follow the naming convention of A-B, where A denotes the network topology, and B denotes the FIB generation. For example, LNet-apsp denotes that the setting is using the LNet, a proprietary network based on the Fabric network architecture [45], and the FIB rules are generated by running an all-pair shortest path algorithm. For CE2D, the settings follow the naming convention of A-B-C[-D], where A denotes the network topology, B denotes the FIB generation, C denotes the property to be verified (all-pair reachability and loop-freeness), and the optional D, if present, indicates that there are long-tail arrivals. For example, I2-OpenR/1buggy-loop-lt represents that 1) the network is using the Internet2 topology; 2) the FIB rules are generated by real OpenR software except for one switch, which is running a buggy OpenR instance; 3) the verifier is configured to check the loop-freeness requirement; and 4) there are long-tail arrivals. The details of the settings are summarized in Table 2.

**Server Configuration.** All evaluations are conducted on cloud Ubuntu servers with 8 vCPUs (2.5GHz) and 32GB memory. The OS is Ubuntu(x64) 18.04.4 LTS with OpenJDK v17.0.3 installed.

**Flash Verifier Implementation.** Flash is implemented in  $\sim$ 4,000 lines of Java code. We release the source code in the form of a library with all presented features. Developers can easily write adapters that feed rule updates to Flash and extend CE2D to achieve customized verification functions.

Flash Device Agent Implementation. Our device agent (if the consistent, early detection feature is needed) can be implemented by patching an open-source modular routing platform adopted in real-world production networks. In particular, we take the open-source routing software OpenR [33] as the platform in our evaluation. OpenR is a state synchronization protocol that stores its state variable (*i.e.*, Adj, Prefix) in a K-V store, and computes the routes using a *Decision* and *Fib* module. Our extension has around 150 lines of C++ code. Through the extension, rule updates computed from the same network state are encapsulated into Thrift [46] messages with tags attached, and are sent to the verification system.

Delta-net and APKeep Implementations. We compare Flash with two state-of-the-art data plane verification systems, Delta-net and APKeep, because their evaluations have demonstrated that they achieve the highest performance. (1) Delta-net\*: Since we do not have access to the source code, we *implement* Delta-net ourselves in Java following the pseudocode in [25]. Given that Delta-net represents each longest-prefix match as an interval, we directly extend it to handle multi-field match and generic ternary match by representing each match as multiple intervals. We use Delta-net\* instead of Delta-net in the results to indicate that it is our implementation. (2) APKeep\*: Similar to Delta-net, APKeep has no open source implementation and we implement APKeep following the pesudocode in [26]. We use APKeep\* to indicate our implementation. We use the default "delay merge" parameter

| Setting            | Total Model Update Time (s) |                   |       | Memory Usage (MB) |         |       | # Predicate Operations (10 <sup>5</sup> ) |                   |       |

|--------------------|-----------------------------|-------------------|-------|-------------------|---------|-------|-------------------------------------------|-------------------|-------|

| Setting            | Delta-net* (speedup)        | APKeep* (speedup) | Flash | Delta-net*        | APKeep* | Flash | Delta-net* (speedup)                      | APKeep* (speedup) | Flash |

| LNet-apsp Subspace | 0.7 (0.3×)                  | 34.1 (15×)        | 2.3   | 29                | 66      | 55    | 6 (0.4×)                                  | 71 (5×)           | 14    |

| LNet-ecmp Subspace | 26 (1.4×)                   | > 36,000 (>1895×) | 19    | 1,249             | > 1,096 | 211   | 281 (20×)                                 | > 9,529 (681×)    | 14    |

| LNet-smr Subspace  | 285 (71×)                   | 1,004 (251×)      | 4     | 6,792             | 31      | 15    | 1,485 (26×)                               | 239 (4×)          | 57    |

| Airtel-trace       | 12 (0.9×)                   | 85 (6.5×)         | 13    | 5                 | 37      | 70    | 141 (141×)                                | 1,321 (1,321×)    | 1     |

| Stanford-trace     | 0.06 (0.5×)                 | 0.58 (4.8×)       | 0.12  | 3                 | 9       | 9     | 1 (1×)                                    | 4.3 (4.3×)        | 1     |

| I2-trace           | <b>0.4</b> (0.3×)           | 6.9 (4.9×)        | 1.4   | 16                | 52      | 52    | 4 (2×)                                    | 56 (28×)          | 2     |

Table 3: Overall performance.

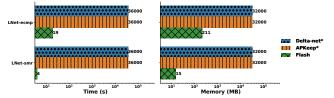

Figure 6: Total model update time (s) and memory consumption (MB) for update storms in baseline settings.

(i.e., 0) in our evaluations. We apply optimizations to Delta-net\* and APKeep\*, and ensure that they have similar results on datasets reported in [25] and [26] respectively.

#### 5.2 Effects of Fast IMT

In this section, we present the evaluation of Fast IMT by focusing on model construction in different network settings.

Baseline: Benefits of Flash upon Update Storms in Largescale Networks with Complex Forwarding Behaviors. We first evaluate Delta-net\*, APKeep\*, and Flash as they are, in our target large-scale networks (LNet-ecmp and LNet-smr), to demonstrate the overall performance gain of Flash. In the baseline evaluation, we generate the updates by putting the rule insertions of all the switches in a sequence, feed the update sequence to the verifier, and measure the execution time and memory consumption to construct the inverse model. We kill the JVM if the execution time exceeds 10 hours. Figure 6 shows the result: Flash (green) finishes in 19 and 4 seconds for LNet-ecmp and LNet-smr respectively, while neither Delta-net\* (blue) nor APKeep\* (orange) can finish within 10 hours. Hence, for LNet-smr, Flash outperforms Delta-net\* and APKeep\* by 9,000× (10 hours divided by 4 seconds). The memory consumption of Flash (green) is also substantially lower (up to 2 orders of magnitude in both settings). While the setting seems extreme, it does happen when the verifier is bootstrapping or running on demand (e.g., for network planning [31, 47] or reachability analysis of Virtual Private Cloud [48]). Thus, we conclude that Flash is fast and memory efficient for data plane verification in large-scale networks. Benefits and Robustness of Fast IMT. Then, we analyze the benefits of Fast IMT as a standalone model construction method, by applying the subspace partition idea to Delta-net\* and APKeep\* in large-scale networks, as subspace partition can be widely effective for large networks. Besides execution time and memory consumption, we also count the number of predicate operations (see §3.3) for each evaluation setting.

The top rows of Table 3 show the results. For example, the row with the name "LNet-smr Subspace" shows the results when subspace partition is applied to all in the LNet-smr. Still, we observe

longer model update time for Delta-net\* and APKeep\*, which is  $1.4\times$  (26s/19s) and >1895× respectively that of Flash in LNet-ecmp, and 71× (285s/4s) and 251× in LNet-smr. The memory footprint of Flash is also smaller in these two settings. For example, Flash uses 15MB in LNet-smr, while Delta-net\* and APKeep\* use 6,792MB and 31MB respectively. Except the LNet-apsp Subspace setting, Flash also reduces the number of predicate operations substantially (20×/681× for Delta-net\* and APKeep\* respectively in LNet-ecmp, and  $26\times/4\times$  in LNet-smr).

For completeness, we next use smaller networks and report the result for three settings widely used in literature: Airtel-trace [25], Stanford-trace [18] and I2-trace [49]. The last 3 rows of Table 3 show the result. We can see that the model update time of APKeep\* is 4.8-6.5× that of Flash. In such smaller networks, Delta-net\* performs the best, with model update time at only 30-90% of Flash. This is true also for some large networks, for example, for LNet-apsp Subspace. However, we see that the number of predicate operations of Delta-net\* is higher (up to 141× in Airtel-trace) than Flash. The efficiency of Delta-net\* comes from its simple, efficient data structure, which works efficiently for prefix-based rules. However, this representation can suffer significant performance degradation for non-prefix rules, as shown in the LNet-smr and LNet-ecmp results; similar degradation results are reported in [26].

Thus, we conclude that Flash is robustly fast under various topologies, FIBs, and update settings. In settings with large networks and complex forwarding behaviors (e.g., LNet-smr and LNet-ecmp), Flash achieves substantial gains compared with the state-of-the-art.

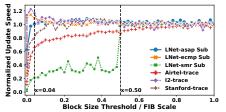

Impact of Block Size Threshold when Cooperating with CE2D. Last, as updates may continuously arrive in practice, Flash may choose to update the inverse model and perform CE2D before processing all the rule updates. This behavior is configured by the block size threshold (BST) parameter *B*, which forces Flash to update the model after processing equal or more than *B* rule updates. To understand how this parameter affects the performance of Flash, we vary the BST value and measure the model construction time for the settings used in Table 3.

Figure 7 shows the results. The x-axis denotes the proportion of the BST value and the FIB scale, as the FIB scale determines the number of updates in our evaluation and varies significantly in each setting. The y-axis is the normalized model update speed, computed as  $T_{\rm baseline}/T_x$ , which categorizes how fast the model update speed is compared to the baseline, where the BST value is infinite and the model is updated after processing all updates. We make the following observations: First, as the threshold increases, the overall trend is that the model update speed will increase and stay at a relatively high level. Second, most settings can reach more than 60% and up to >100% (LNet-apsp, LNet-ecmp, and I2-trace) efficiency

Figure 7: Effects of block size threshold on the model update speed.

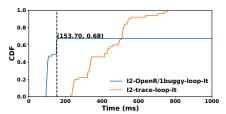

Figure 8: Timeline of FIB updates and Figure 9: CE2D verification report time. verification reports.

of the baseline with  $x \approx 0.04$ . The only exception is LNet-ecmp Subspace, which only reaches  $\sim 0.2$  when  $x \approx 0.04$  and > 0.8 when  $x \approx 0.5$ . However, as the speed-up of Flash in LNet-smr Subspace is  $> 70 \times$ , Flash can still be as  $> 14 \times$  fast as the state-of-the-art. Thus, we conclude that Fast IMT is more efficient with a larger block size threshold. However, performance improvements can still be obtained when the threshold is no less than 4% of the FIB scale.

### 5.3 Effects of CE2D

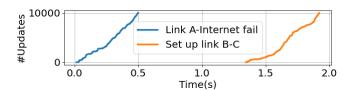

Now we present the evaluation results of CE2D to demonstrate its efficacy, performance benefits, and robustness in extreme settings. Ability to Achieve Consistent Early Detection. We first conduct an evaluation to verify that CE2D can provide consistent early detection results. Specifically, we run a simulation using the I2-OpenR-loop setting. We use Mininet [50] to construct a network with the Internet2 topology. A real OpenR instance is running on each switch and connects to Flash through the host network. We trigger the FIB computation by bringing down two links (chic-alta and chic-kans) consecutively in Mininet. We compare CE2D with two strategies: (1) per-update verification (PUV), which checks the property after processing a single rule update (e.g., [18, 25, 26]), and (2) block-update verification (BUV), which checks the property after processing a block of updates (e.g., [47]). We record on the verifier the time of the FIB updates from each switch, and the time when the verifier reports a deterministic result.

The results are shown in Figure 8. A cross point (x,y) represents that the FIB update of switch y is received at time x since the link down events are triggered, and the color indicates the epoch tag. A dot point (x,y) represents that the verifier strategy y reports a deterministic result at time x, where orange indicates a loop and blue indicates no loops. As we can see, the two simultaneous link failures trigger the FIB re-computation multiple times on each switch. With both PUV and BUV, the verifier reports two transient loops (the orange dots), which is inconsistent with the final verification result. Meanwhile, Flash does not report false-positive errors and guarantees that the verification result is consistent.

Benefits of CE2D upon Long-tail Arrivals. One may question how much performance the CE2D can improve when long-tail arrivals happen. Thus, we evaluate the effects of CE2D in two settings where loops occur: I2-OpenR/1buggy-loop-lt, I2-trace-loop-lt. For each setting, we run 50 independent random trials and in each trial, we simulate the long-tail effect by configuring one random node to delay 60s before sending the updates. We measure the time when Flash reports a deterministic result.

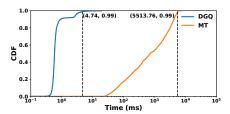

The results are shown in Figure 9. The x-axis is the report time and the y-axis is the Cumulative Distribution Function (CDF). We limit the range of the x-axis to [0ms, 1,000ms]: if a curve does not reach y=1 at 1,000ms, the result is achieved at 60s, *i.e.*, after receiving the updates from the dampened node. We see in the figure that point (153.7ms, 0.68) is on the curve of I2-OpenR/1buggy-loop-lt, indicating that Flash can detect the loop in less than 153.7ms in 68% of the trials, which is substantially smaller (> 390×) than the 60s baseline. In I2-trace-loop-lt, Flash can detect the loop early within 760ms in all the trials, yielding a 79x speed-up. Thus, we conclude that the improvement of CE2D can be quite common (68% to 100%) and substantial (79 to > 390) upon long-tail arrivals.

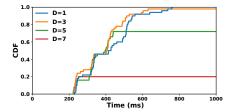

Effects of Multiple Dampened Switches. Now we investigate the effects of CE2D when there are multiple dampened switches. We use the I2-trace-loop-lt setting, which uses the real network topology and update sequence from the Internet2 dataset. We enumerate the number of dampened devices D from 1 to 7. For each D, we configure Flash to check loops using CE2D and run 50 independent random trials. The results are shown in Figure 10. In 72.5% (*i.e.*, 145/200) of the cases, Flash can detect consistent loops within 800ms, 75× as fast as a complete verification. dampened devices D grows, the probability of successful consistent early detection becomes lower. For example, CE2D can still detect the error within 800ms in more than 90% of the cases when  $D \leq 3$ , and in ~20% of the cases when D = 7, *i.e.*, 77.8% of the switches are dampened. Thus, we conclude that CE2D can detect errors early even with limited and partial knowledge of the data plane.

#### 5.4 Micro Benchmark

In this section, we present micro benchmarks that evaluate the effects of several optimization techniques in Flash.

**Effects of PAT in Large-scale Networks.** We show the effects of persistent action tree (PAT, see §3.4) by analyzing the results in Table 3. Note that the total model update time includes both the time to create and delete equivalence classes (denoted as  $T_{EC}$ , which is handled by the persistent action tree (PAT) in Flash (§3.4) and independent of the number of predicate operations, and the time to process the predicates (denoted as  $T_{OP}$ ). In Table 3, we see that the model construction time improvement is larger than the #predicate operations improvement of Flash over APKeep\* in the top 3 large-scale network settings, e.g., 15x and 5x for LNet-apsp respectively. The reason is that in smaller networks, the model construction time is dominated by  $T_{OP}$ , and the performance gain mainly comes

different number of dampened switches. struction for I2-trace.

Figure 10: Early loop detection time for Figure 11: Time breakdown of model con- Figure 12: Execution time of all-pair ToRto-ToR reachability check.

from the reduction of #predicate operations<sup>10</sup>. Meanwhile, in large networks, T<sub>EC</sub> becomes dominant in the overall performance, and Flash benefits more from the performance gain of PAT.

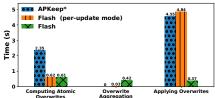

Effects of MR2. To better understand how MR2 (§3.2) contributes to the overall performance gain of Flash, we conduct a breakdown analysis of the 3 phases in the model construction: computing atomic overwrites (Map), overwrite aggregation (i.e., Reduce I/II), and applying overwrites. We measure the total time of each phase for APKeep\*, Flash and a variant of Flash, referred to as Flash (per-update mode), where the block size threshold is set to 1.

Figure 11 shows the time breakdown of APKeep\*, Flash (perupdate mode) and Flash in the I2-trace setting. While Flash introduces some overhead of overwrite aggregation (0.42s), computing atomic overwrites (3.85×) and applying overwrites (12.30×) are accelerated compared with APKeep\*. Note that it takes longer to apply the overwrites in Flash (per-update mode) (4.84s) than APKeep\* (4.55s) because the cross product computation is not optimized for a single rule update. Thus, we conclude that with overwrite aggregation, MR2 enables Flash to improve the performance by substantially reducing the time to compute the atomic conflict-free model overwrites and to apply the aggregated overwrites.

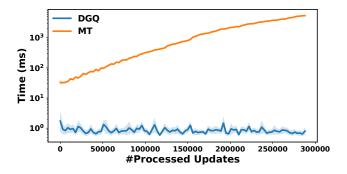

Efficiency of Decremental Verification Graph. Last, we show the efficiency of performing consistent early detection for regularexpression-based requirements using the decremental verification graph approach (§4.2). Specifically, we use the LNet-apsp Subspace setting and check all-pair ToR-to-ToR reachability. Flash generates 5,376 verification graphs in total, and 48 verification graphs for each subspace verifier. The rule insertions of each switch are packed as a batch. We verify the reachability after processing each batch, and measure the execution time of the verification for a single subspace verifier using (1) the decremental graph query (DGQ, see §4.2) approach, and (2) model traversal (MT, i.e., traversing the model from each source ToR using depth-first traversal).

Figure 12 shows the CDF of verification time. We can see that DGQ (blue) is closer to the y-axis than MT (orange). The median, mean, 99-percentile, and maximum time of DGQ and MT are 0.58/0.84/4.74/19.57ms and 772.98/1,522.22/5,513.76/7,466.87ms respectively. Compared with MT, Flash improves the 99-percentile execution time by  $\sim$ 1,163× (4.74ms v.s. 5,513.76ms). Thus, we can conclude that the decremental verification graph approach substantially improves the verification performance of regular expression based requirements and enables efficient consistent early detection.

# **Computational Overhead Quantification**

One concern is that Flash may have large computational overheads and hence demand a large amount of computational resources. To quantify the demand, we consider the resource overhead and operational cost of the largest setting in Table 2: LNet-ecmp (6,016 nodes and  $3.7 \times 10^7$  rules). We consider two deployment settings.

We first evaluate the setting of deploying dedicated servers for continuous verification. For LNet-ecmp, Flash partitions a subspace for each pod and hence has a total of 112 subspaces. Each subspace verifier requires 1 (v)CPU, 211MB memory for the inverse model, and 336MB memory for the verification graphs to check all-pair-ToR reachability, and each machine requires <4GB memory to run the JVM and store the rules. Thus, the total computation overhead is 112 (v)CPUs, <62GB (61.26GB) (for model and verification graphs) + 4GB (for rules and JVM) memory. If the subspace verifiers are deployed on k machine with dedicated resources, each machine requires  $\lceil \frac{112}{k} \rceil$  (v)CPUs and  $\lceil \frac{62}{k} \rceil$  + 4GB memory. To get a sense of the cost of the resources in a data center, we apply the availability and pricing of AWS EC2 (US Ohio) [52] on 2022/7/1, to obtain that Flash needs 4 c6g.8xlarge (32 vCPUs and 64GB memory) instances. The estimated cost is \$2.74/hour.

We next evaluate the one-shot deployment setting where an operator uses on-demand computation resources to verify LNet-ecmp. Also selecting 4 c6g.8xlarge (32 vCPUs and 64GB memory) instances, Flash completes the one-shot verification in 21s: 1s to receive the rule updates, 19s for model construction, and 939ms for reachability check. Assuming each instance stays up for 1 minute and using AWS pricing data, the system costs \$4.352/hour or \$0.07/run.

# **RELATED WORK**

We now discuss related studies in various fields that motivate the design and implementation of Flash.